APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 7

Subject : Computer System Architecture

Year : 2018

Term : DECEMBER

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 405

Page:1

= R7954 சடா Pagesr3 ہے

# சல்

Reg No.: Name: പഞ്ഞ ಹಾ

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY ` = =

SEVENTH SEMESTER B.TECH DEGREE EXAMINATION, DECEMBER 2018

Course Code: CS405

Course Name: COMPUTER SYSTEM ARCHITECTURE

Max. Marks: 100 Duration: 3 Hours

PART A

Answer all questions, each carries 4 marks. Marks

1 With a neat sketch, explain the architecture of a vector supercomputer. (4)

2 Explain implicit and explicit parallelism in parallel programming (4)

3 Compare the characteristics of CISC and RISC Architectures (4)

4 Differentiate between crossbar network and multiport memory. (4)

5 How does cache inconsistency occur in caches due to process migration and (4)

1೦?

6 Differentiate between store and forward and wormhole routing (4)

7 What are the possible hazards that can occur between read and write (4)

operations in an instruction pipeline?

8 Determine the frequency of the pipeline if the stage delays are رع = 315, ८ = 73 (4)

“515 and t4=8 ns and the latch delay is 1 ns.

9 Distinguish between static dataflow computers and dynamic dataflow (4)

computers.

10 What are the four context switching polices for multithreaded architecture? (4)

PART B

Answer any two full questions, each carries 9 marks.

11 a) Explain Flynn’s classification of computer architecture (4)

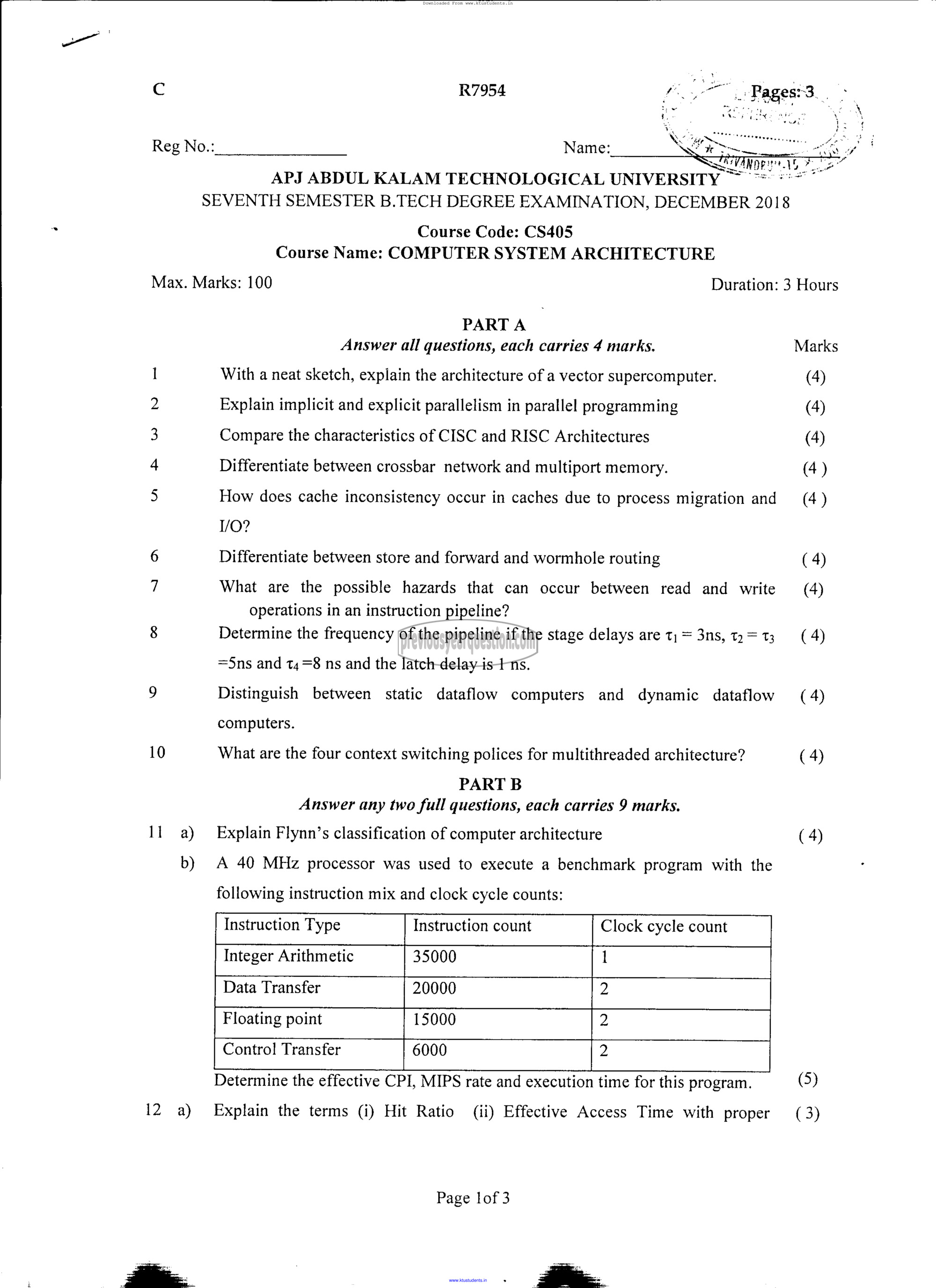

b) A 40 MHz processor was used to execute a benchmark program with the

following instruction mix and clock cycle counts:

Instruction count Clock cycle count

35000

20000

Instruction Type

Integer Arithmetic

Data Transfer

Floating point

Contro! Transfer

Determine the effective CPI, MIPS rate and execution time for this program. (5)

12 ൭ Explain the terms (i) Hit Ratio (ii) Effective Access Time with proper (3)

Page lof 3