APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 7

Subject : Computer System Architecture

Year : 2018

Term : DECEMBER

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 405

Page:2

13

15

b)

a)

b)

a)

b)

a)

b)

R7954 Pages: 3

equations

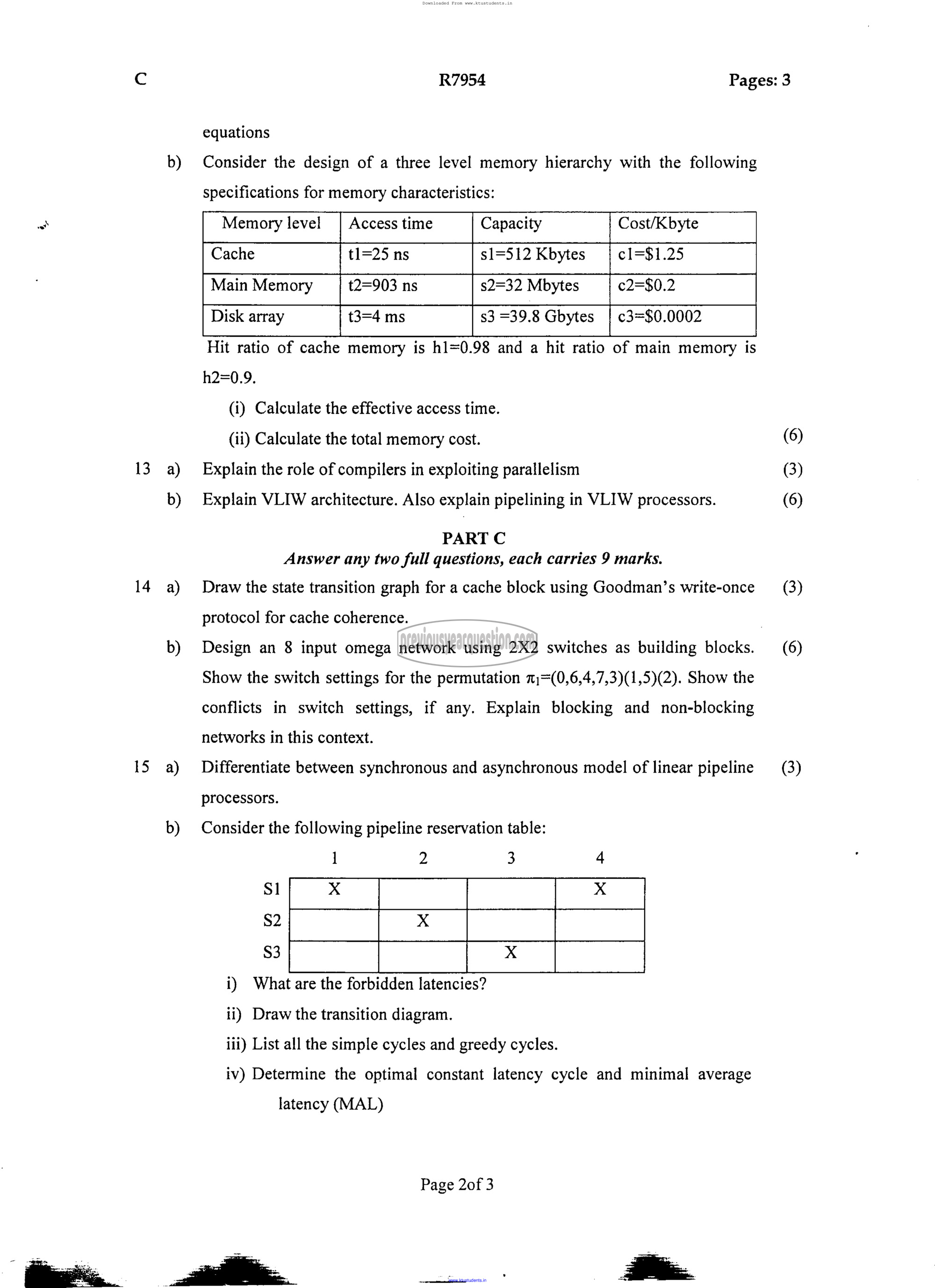

Consider the design of a three level memory hierarchy with the following

specifications for memory characteristics:

Memory level

Access time | Capacity Cost/Kbyte

Cache tl=25 ns 51-512 Kbytes | cl=$1.25

125903 ns s2=32 Mbytes c2=$0.2

(3-4 ms s3 =39.8 Gbytes | c3=$0.0002

Hit ratio of cache memory is h1=0.98 and a hit ratio of main memory is

h2=0.9.

(i) Calculate the effective access time.

(ii) Calculate the total memory cost.

Explain the role of compilers in exploiting parallelism

Explain VLIW architecture. Also explain pipelining in VLIW processors.

PART (^

Answer any two full questions, each carries 9 marks.

Draw the state transition graph for a cache block using Goodman’s write-once

protocol for cache coherence.

Design an 8 input omega network using 2X2 switches as building blocks.

Show the switch settings for the permutation 2)=(0,6,4,7,3)(1,5)(2). Show the

conflicts in switch settings, if any. Explain blocking and non-blocking

networks in this context.

Differentiate between synchronous and asynchronous model of linear pipeline

processors.

Consider the following pipeline reservation table:

i) What are the forbidden latencies?

ii) Draw the transition diagram.

iii) List all the simple cycles and greedy cycles.

iv) Determine the optimal constant latency cycle and minimal average

latency (MAL)

Page 2of 3

(6)

(3)

(6)

(3)

(6)

(3)