APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 4

Subject : Computer Organization and Architecture

Year : 2018

Term : DECEMBER

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 202

Page:1

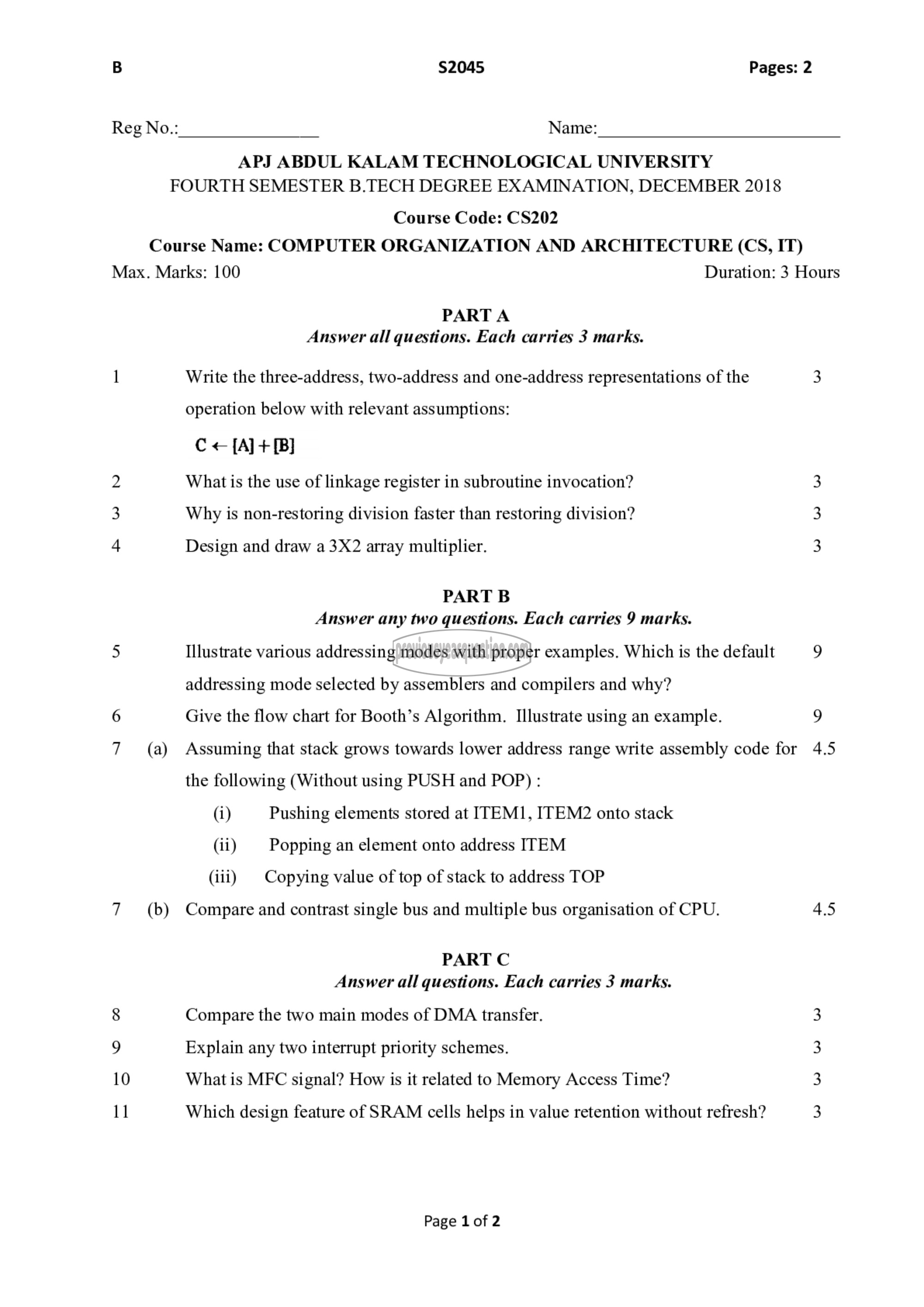

B $2045 Pages: 2

Reg No.: Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

FOURTH SEMESTER B.TECH DEGREE EXAMINATION, DECEMBER 2018

Course Code: CS202

Course Name: COMPUTER ORGANIZATION AND ARCHITECTURE (CS, IT)

Max. Marks: 100 Duration: 3 Hours

PARTA

Answer all questions. Each carries 3 marks.

1 Write the three-address, two-address and one-address representations of the 3

operation below with relevant assumptions:

€ < [A] + [8]

2 What is the use of linkage register in subroutine invocation? 3

3 Why is non-restoring division faster than restoring division? 3

4 Design and draw a 3X2 array multiplier. 3

PART B

Answer any two questions. Each carries 9 marks.

5 Illustrate various addressing modes with proper examples. Which is the default 9

addressing mode selected by assemblers and compilers and why?

6 Give the flow chart for Booth’s Algorithm. Illustrate using an example. 9

7 (2) Assuming that stack grows towards lower address range write assembly code for 4.5

the following (Without using PUSH and POP) :

(i) Pushing elements stored at ITEM1, ITEM2 onto stack

(ii) | Popping an element onto address ITEM

(iii) | Copying value of top of stack to address TOP

7 (७) Compare and contrast single bus and multiple bus organisation of CPU. 4.5

PART C

Answer all questions. Each carries 3 marks.

8 Compare the two main modes of DMA transfer. 3

9 Explain any two interrupt priority schemes. 3

10 What is MFC signal? How is it related to Memory Access Time? 3

11 Which design feature of SRAM cells helps in value retention without refresh? 3

Page 1 of 2