APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 4

Subject : Computer Organization

Year : 2017

Term : JUNE

Scheme : 2015 Full Time

Course Code : EC 206

Page:1

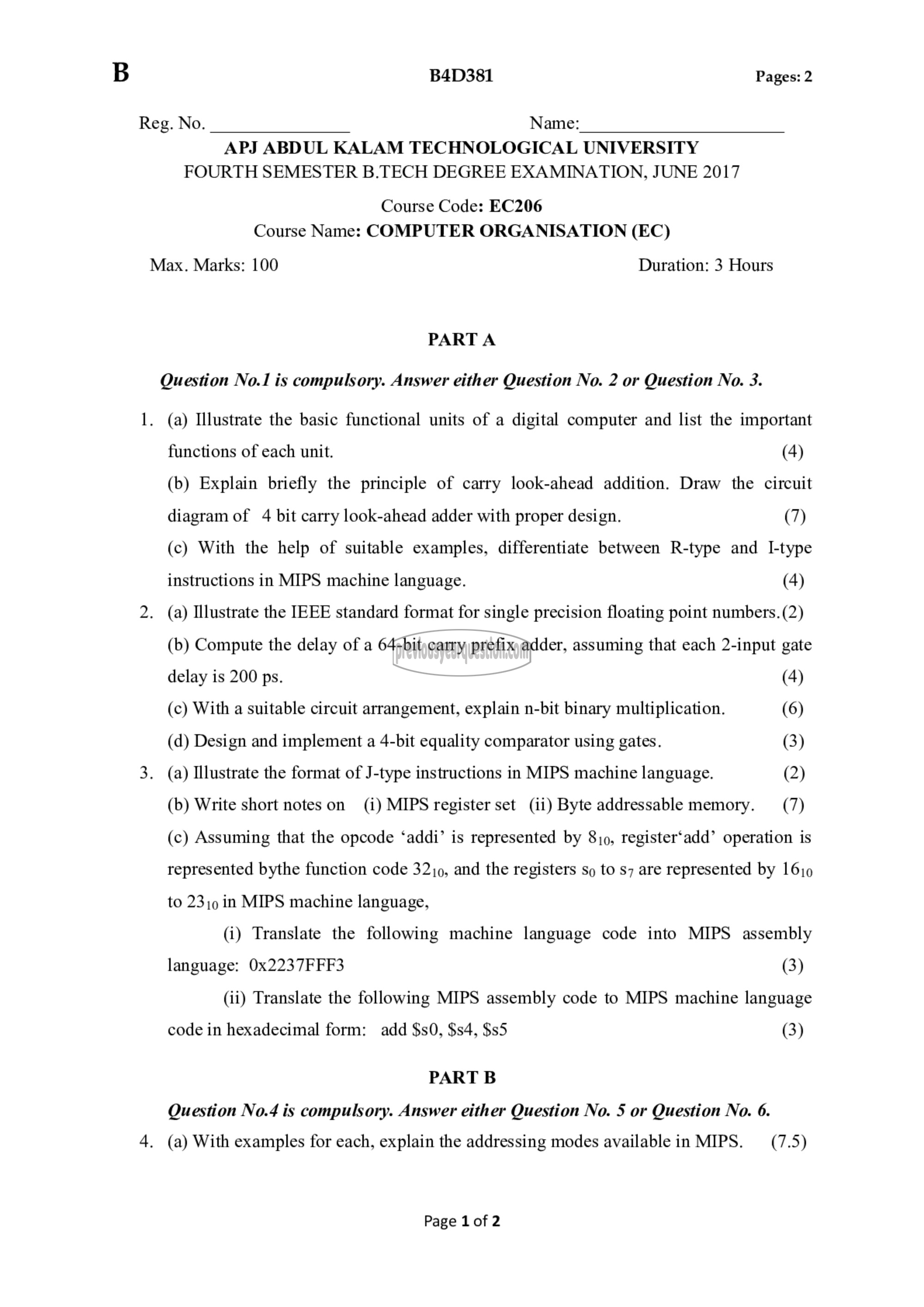

B

Reg. No. Name:

B4D381 Pages: 2

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

FOURTH SEMESTER B.TECH DEGREE EXAMINATION, JUNE 2017

Course Code: EC206

Course Name: COMPUTER ORGANISATION (EC)

Max. Marks: 100 Duration: 3 Hours

PARTA

Question No.1 is compulsory. Answer either Question No. 2 or Question No. 3.

. (a) Illustrate the basic functional units of a digital computer and list the important

functions of each unit. (4)

(b) Explain briefly the principle of carry look-ahead addition. Draw the circuit

diagram of 4 bit carry look-ahead adder with proper design. (7)

(c) With the help of suitable examples, differentiate between R-type and I-type

instructions in MIPS machine language. (4)

. (a) Illustrate the IEEE standard format for single precision floating point numbers. (2)

(b) Compute the delay of a 64-bit carry prefix adder, assuming that each 2-input gate

delay is 200 ps. (4)

(c) With a suitable circuit arrangement, explain n-bit binary multiplication. (6)

(d) Design and implement a 4-bit equality comparator using gates. (3)

. (a) Illustrate the format of J-type instructions in MIPS machine language. (2)

(b) Write short notes on (1) MIPS register set (ii) Byte addressable memory. (7)

(0) Assuming that the opcode ‘addi’ is represented by 810, register‘add’ operation is

represented bythe function code 3210, and the registers 50 to 57 are represented by 1610

to 2310 in MIPS machine language,

(i) Translate the following machine language code into MIPS assembly

language: 0x2237FFF3 (3)

(ii) Translate the following MIPS assembly code to MIPS machine language

code in hexadecimal form: add $s0, $s4, $s5 (3)

PART 8

Question No.4 is compulsory. Answer either Question No. 5 or Question No. 6.

4. (a) With examples for each, explain the addressing modes available in MIPS. (7.5)

Page 1 of 2