APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 7

Subject : Computer System Architecture

Year : 2019

Term : MAY

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 405

Page:1

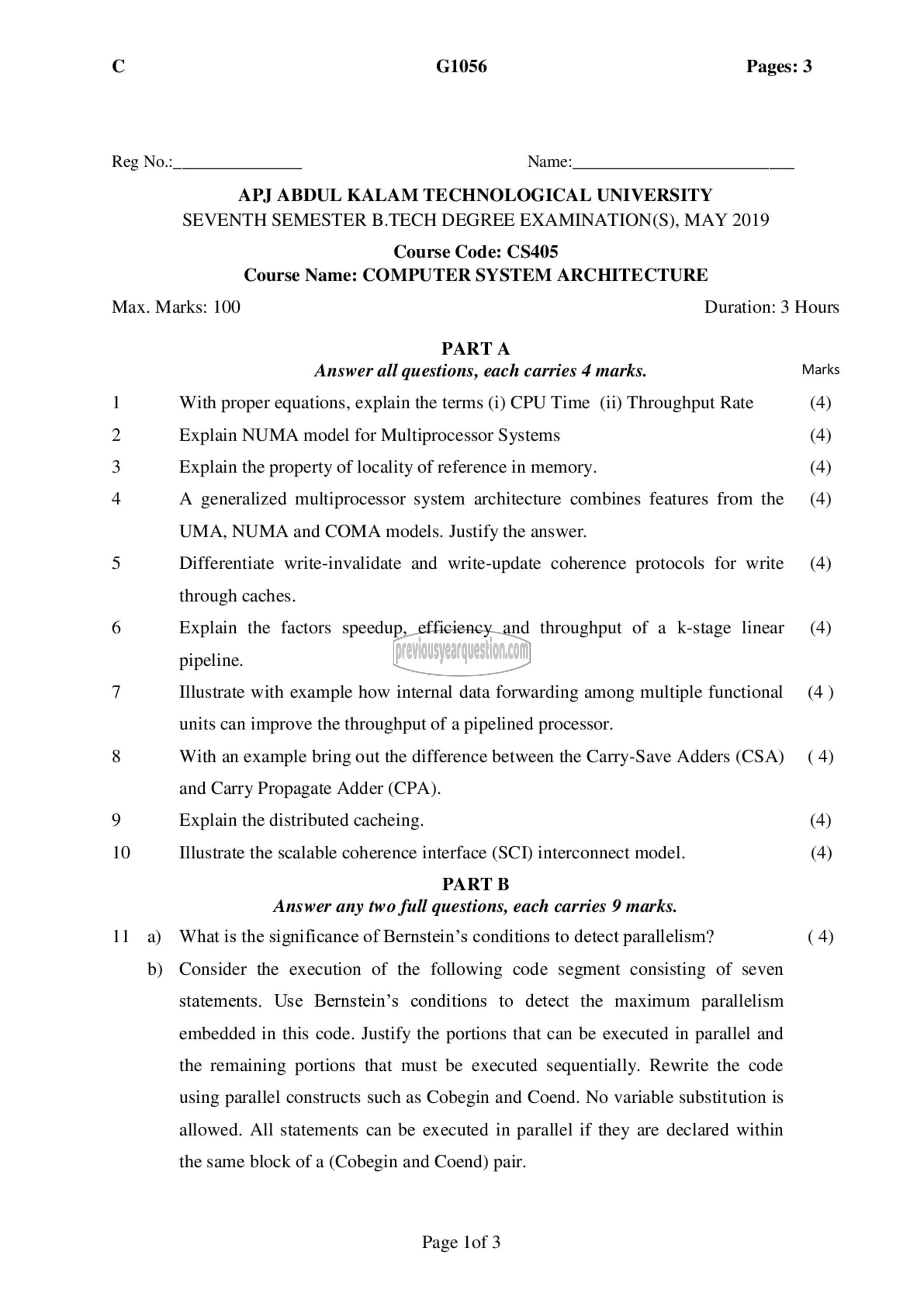

Cc G1056 Pages: 3

Reg No.:_ Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

SEVENTH SEMESTER B.TECH DEGREE EXAMINATION(S), MAY 2019

Course Code: CS405

Course Name: COMPUTER SYSTEM ARCHITECTURE

Max. Marks: 100 Duration: 3 Hours

PARTA

Answer all questions, each carries 4 marks. Marks

1 With proper equations, explain the terms (i) CPU Time (ii) Throughput Rate (4)

2 Explain NUMA model for Multiprocessor Systems (4)

3 Explain the property of locality of reference in memory. (4)

+ A generalized multiprocessor system architecture combines features from the (4)

UMA, NUMA and COMA models. Justify the answer.

5 Differentiate write-invalidate and write-update coherence protocols for write (4)

through caches.

6 Explain the factors speedup, efficiency and throughput of a k-stage linear (4)

pipeline.

7 Illustrate with example how internal data forwarding among multiple functional (4)

units can improve the throughput of a pipelined processor.

8 With an example bring out the difference between the Carry-Save Adders (CSA) (4)

and Carry Propagate Adder (CPA).

9 Explain the distributed cacheing. (4)

10 Illustrate the scalable coherence interface (SCI) interconnect model. (4)

PART 13

Answer any two full questions, each carries 9 marks.

11 a) What 15 the significance of Bernstein’s conditions to detect parallelism? (4)

b) Consider the execution of the following code segment consisting of seven

statements. Use Bernstein’s conditions to detect the maximum parallelism

embedded in this code. Justify the portions that can be executed in parallel and

the remaining portions that must be executed sequentially. Rewrite the code

using parallel constructs such as Cobegin and Coend. No variable substitution is

allowed. All statements can be executed in parallel if they are declared within

the same block of a (Cobegin and Coend) pair.

Page lof 3