APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 7

Subject : Computer System Architecture

Year : 2019

Term : MAY

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 405

Page:2

12 a)

b)

13 a)

b)

14 ಬ

b)

15 a)

b)

G1056 Pages: 3

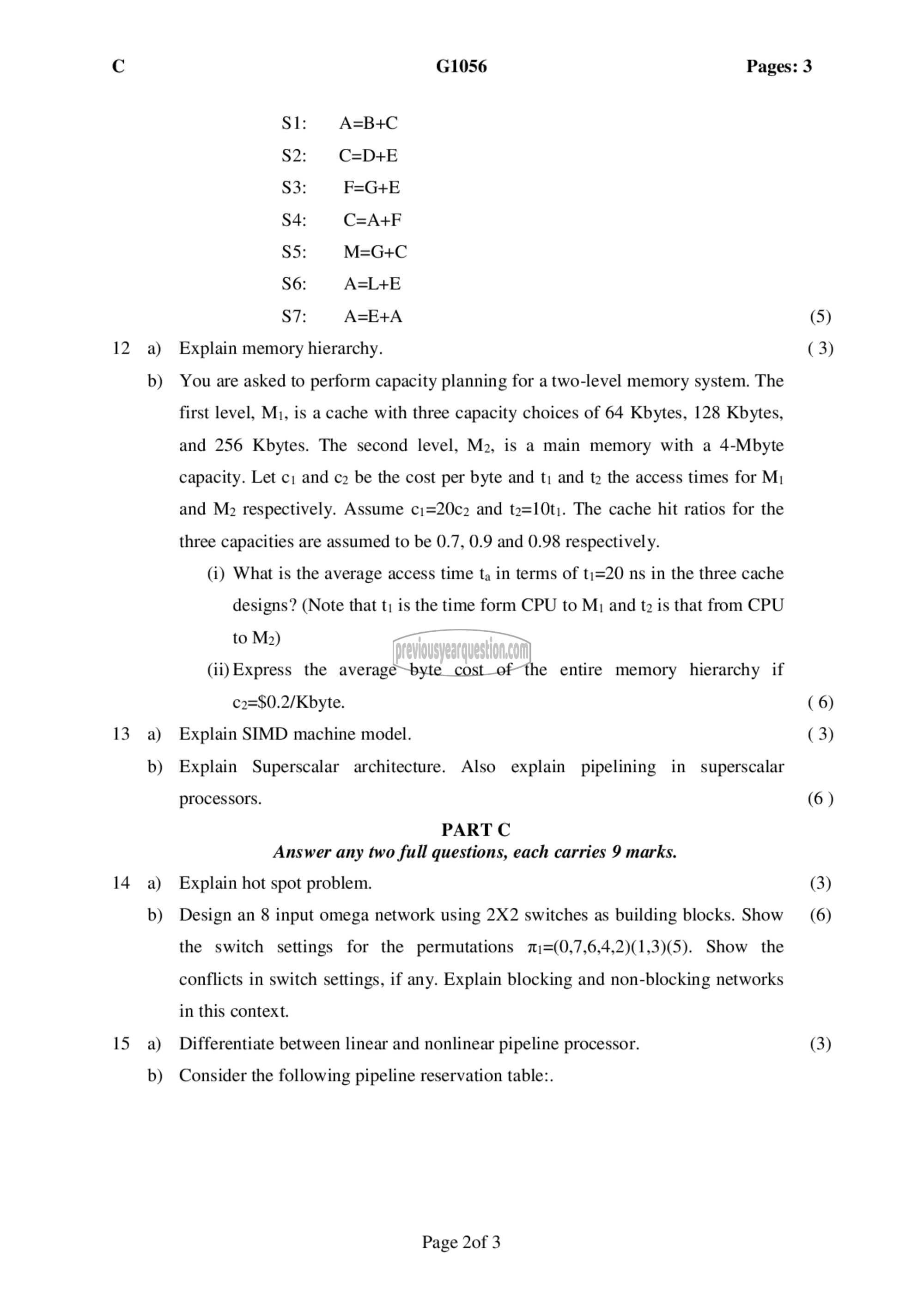

51: A=B+C

52: (=+

53: F=G+E

S4: C=A+F

95; M=G+C

56: A=L+E

S7: A=E+A (5)

Explain memory hierarchy. (3)

You are asked to perform capacity planning for a two-level memory system. The

first level, Mi, is a cache with three capacity choices of 64 Kbytes, 128 Kbytes,

and 256 Kbytes. The second level, M2, is a main memory with a 4-Mbyte

capacity. Let c; and دہ be the cost per byte and 11 and جا the access times for ۸

and M2 respectively. Assume c;=20c2 and t2=10ti. The cache hit ratios for the

three capacities are assumed to be 0.7, 0.9 and 0.98 respectively.

(i) What is the average access time ta in terms of 1520 ns in the three cache

designs? (Note that 11 is the time form CPU to M; and tz is that from CPU

to M2)

(ii)Express the average byte cost of the entire memory hierarchy if

c2=$0.2/Kbyte.

Explain SIMD machine model.

Explain Superscalar architecture. Also explain pipelining in superscalar

processors.

PART C

Answer any two full questions, each carries 9 marks.

Explain hot spot problem.

Design an 8 input omega network using 2X2 switches as building blocks. Show

the switch settings for the permutations 71ಎ(0,7,6,4,2)(1,3)(5). Show the

conflicts in switch settings, if any. Explain blocking and non-blocking networks

in this context.

Differentiate between linear and nonlinear pipeline processor.

Consider the following pipeline reservation table:.

Page 2of 3

(6)

(3)

(6)

(3)

(6)

(3)