APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 7

Subject : Computer System Architecture

Year : 2019

Term : MAY

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 405

Page:3

16

17

18

19

a)

b)

a)

b)

a)

b)

a)

b)

G1056 Pages: 3

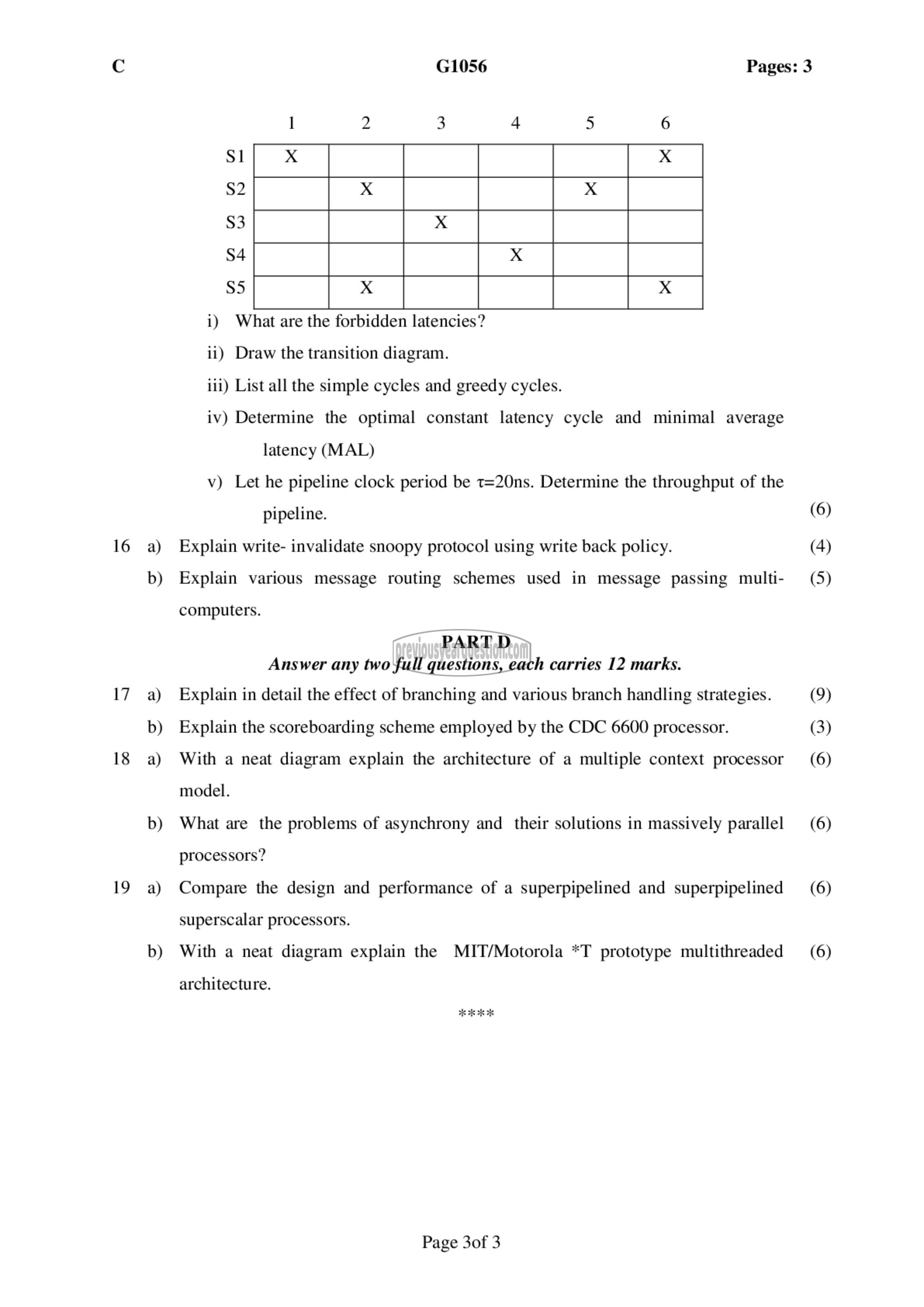

i) What are the forbidden latencies?

ii) Draw the transition diagram.

iii) List all the simple cycles and greedy cycles.

iv) Determine the optimal constant latency cycle and minimal average

latency (MAL)

v) Let he pipeline clock period be t=20ns. Determine the throughput of the

pipeline.

Explain write- invalidate snoopy protocol using write back policy.

Explain various message routing schemes used in message passing multi-

computers.

PART 0

Answer any two full questions, each carries 12 marks.

Explain in detail the effect of branching and various branch handling strategies.

Explain the scoreboarding scheme employed by the CDC 6600 processor.

With a neat diagram explain the architecture of a multiple context processor

model.

What are the problems of asynchrony and _ their solutions in massively parallel

processors?

Compare the design and performance of a superpipelined and superpipelined

superscalar processors.

With a neat diagram explain the MIT/Motorola *T prototype multithreaded

architecture.

RE

Page 3083

(6)

(4)

(5)

(9)

(3)

(6)

(6)

(6)

(6)