APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Switching Theory and Logic Design

Year : 2018

Term : DECEMBER

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 203

Page:1

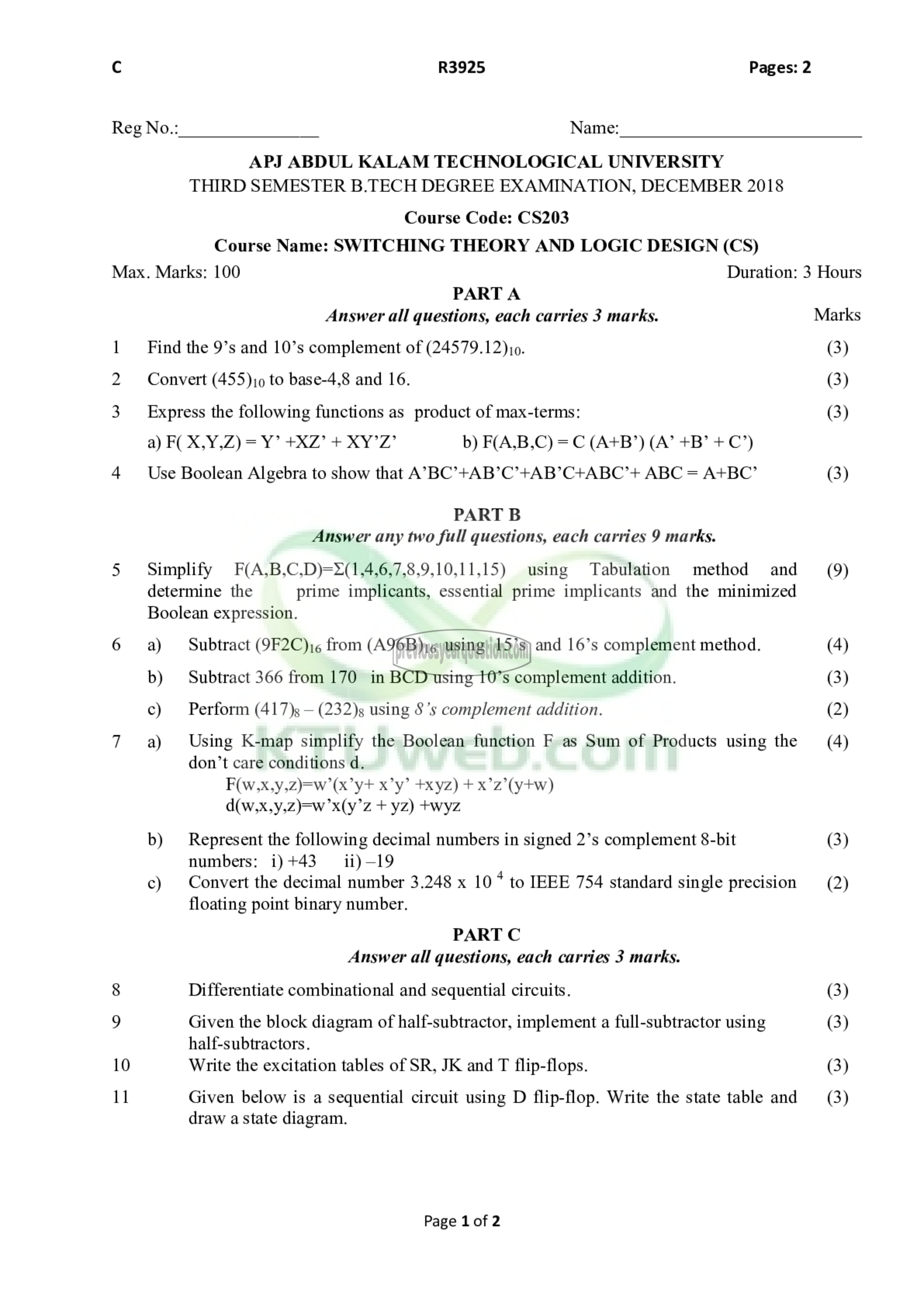

€ ௩3925 Pages: 2

Reg No.: Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

THIRD SEMESTER B.TECH DEGREE EXAMINATION, DECEMBER 2018

Course Code: ೮5203

Course Name: SWITCHING THEORY AND LOGIC DESIGN (CS)

Max. Marks: 100 Duration: 3 Hours

PART A

Answer all questions, each carries 3 marks. Marks

1 Find the 9’s and 10’s complement of (24579.12)10. (3)

2 Convert (455) 1௦ base-4,8 and 16. (3)

3 Express the following functions as product of max-terms: (3)

a) F( X,Y,Z) = Y’ +XZ’ + XY’Z’ 0) F(A,B,C) = © (A+B’) (^ ` +B’ + C’)

4 പടം Boolean Algebra to show that A7BC’+AB’C’+AB’C+ABC’+ ABC = A+BC’ (3)

PART B

Answer any two full questions, each carries 9 marks.

5 Simplify F(A,B,C,D)==(1,4,6,7,8,9,10,11,15) using Tabulation method and (9)

determine the prime implicants, essential prime implicants and the minimized

Boolean expression.

6 ஐ Subtract (9F2C)ji¢ from (49618) using 15’s and 16’s complement method. (4)

b) Subtract 366 from 170 in BCD using 10’s complement addition. (3)

c) Perform (417), - (232); using 8 ' complement addition. (2)

7 8) Using K-map simplify the Boolean function F as Sum of Products using the (4)

don’t care conditions 6,

F(w,x,y,Z)=w’ (x’y+ x’y’ +xyz) + x’z’(ytw)

d(w.x,y.Z)=w’x(y’z + yz) +wyz

b) Represent the following decimal numbers in signed 2’s complement 8-bit (3)

numbers: 1) +43 1)-19

c) Convert the decimal number 3.248 x 10 4 to IEEE 754 standard single precision (2)

floating point binary number.

PART C

Answer all questions, each carries 3 marks.

8 Differentiate combinational and sequential circuits. (3)

9 Given the block diagram of half-subtractor, implement a full-subtractor using (3)

half-subtractors.

10 Write the excitation tables of SR, JK and T flip-flops. (3)

11 Given below is a sequential circuit using D flip-flop. Write the state table and (3)

draw a state diagram.

Page 1 of 2