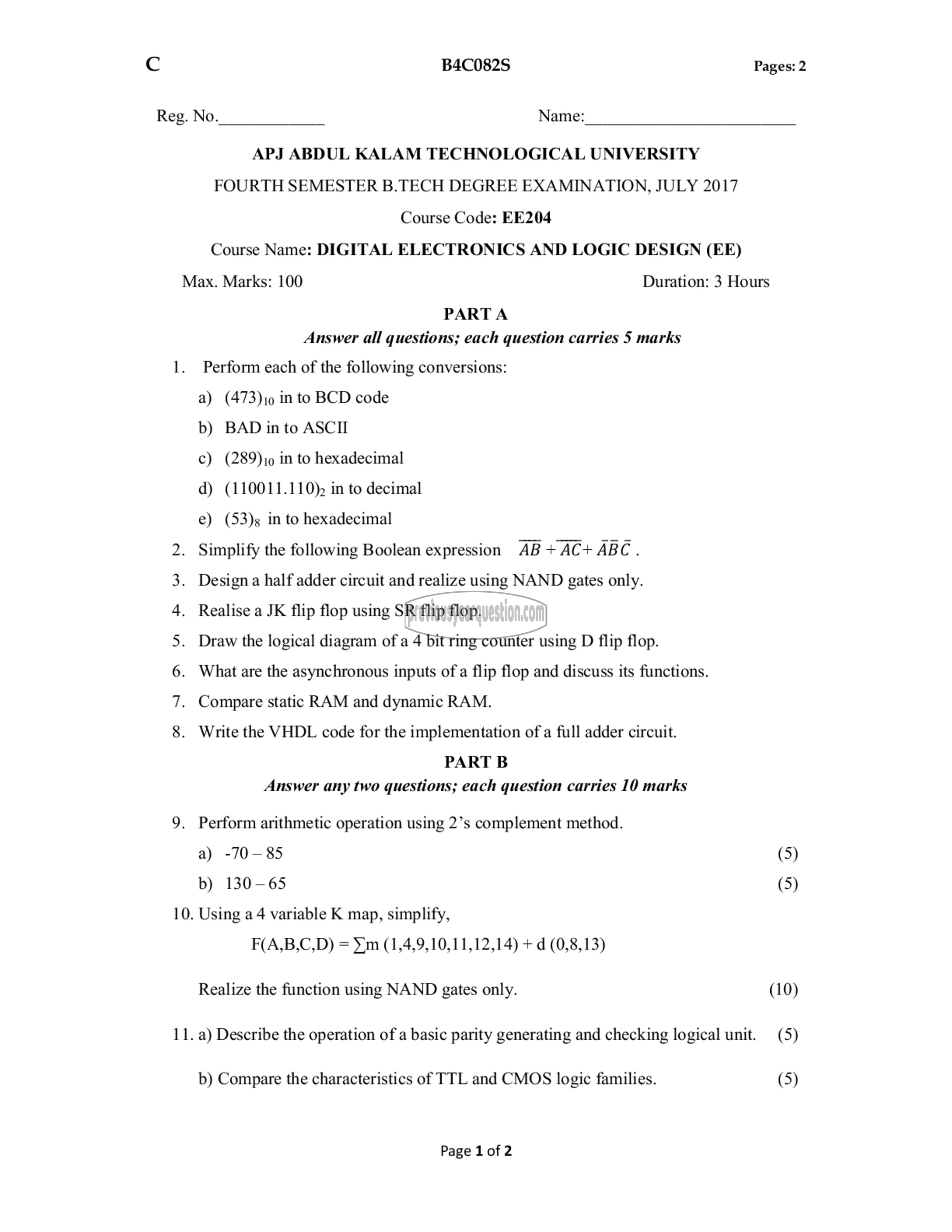

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 4

Subject : Digital Electronics and Logic Design

Year : 2017

Term : JULY

Scheme : 2015 Full Time

Course Code : EE 204

Page:1

(0

Reg. No. Name:

Max. Marks: 100

69 > naw & ம்

೫400825

Pages: 2

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

FOURTH SEMESTER B.TECH DEGREE EXAMINATION, JULY 2017

Course Code: EE204

Course Name: DIGITAL ELECTRONICS AND LOGIC DESIGN (EE)

PARTA

Answer all questions; each question carries 5 marks

Perform each of the following conversions:

a) (473), in to BCD code

b) BAD in to ASCII

௦) (289) in to hexadecimal

d) (110011.110)) in to decimal

e) (53% in to hexadecimal

Simplify the following Boolean expression AB + 46+ ABC.

Design a half adder circuit and realize using NAND gates only.

Realise a JK flip flop using SR flip flop.

Draw the logical diagram of a 4 bit ring counter using D flip flop.

What are the asynchronous inputs of a flip flop and discuss its functions.

Compare static RAM and dynamic RAM.

Write the VHDL code for the implementation of a full adder circuit.

PART B

Answer any two questions; each question carries 10 marks

Perform arithmetic operation using 2’s complement method.

a) -70-85

b) 130-65

. Using a 4 variable K map, simplify,

F(A,B,C,D) = ௩ (1,4,9,10,11,12,14) + d (0,8, 13)

Realize the function using NAND gates only.

. a) Describe the operation of a basic parity generating and checking logical unit.

b) Compare the characteristics of TTL and CMOS logic families.

Page 1 of 2

Duration: 3 Hours

(5)

(5)

(10)

(5)

(5)