APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 4

Subject : Digital Electronics and Logic Design

Year : 2017

Term : JULY

Scheme : 2015 Full Time

Course Code : EE 204

Page:2

B4C082S Pages: 2

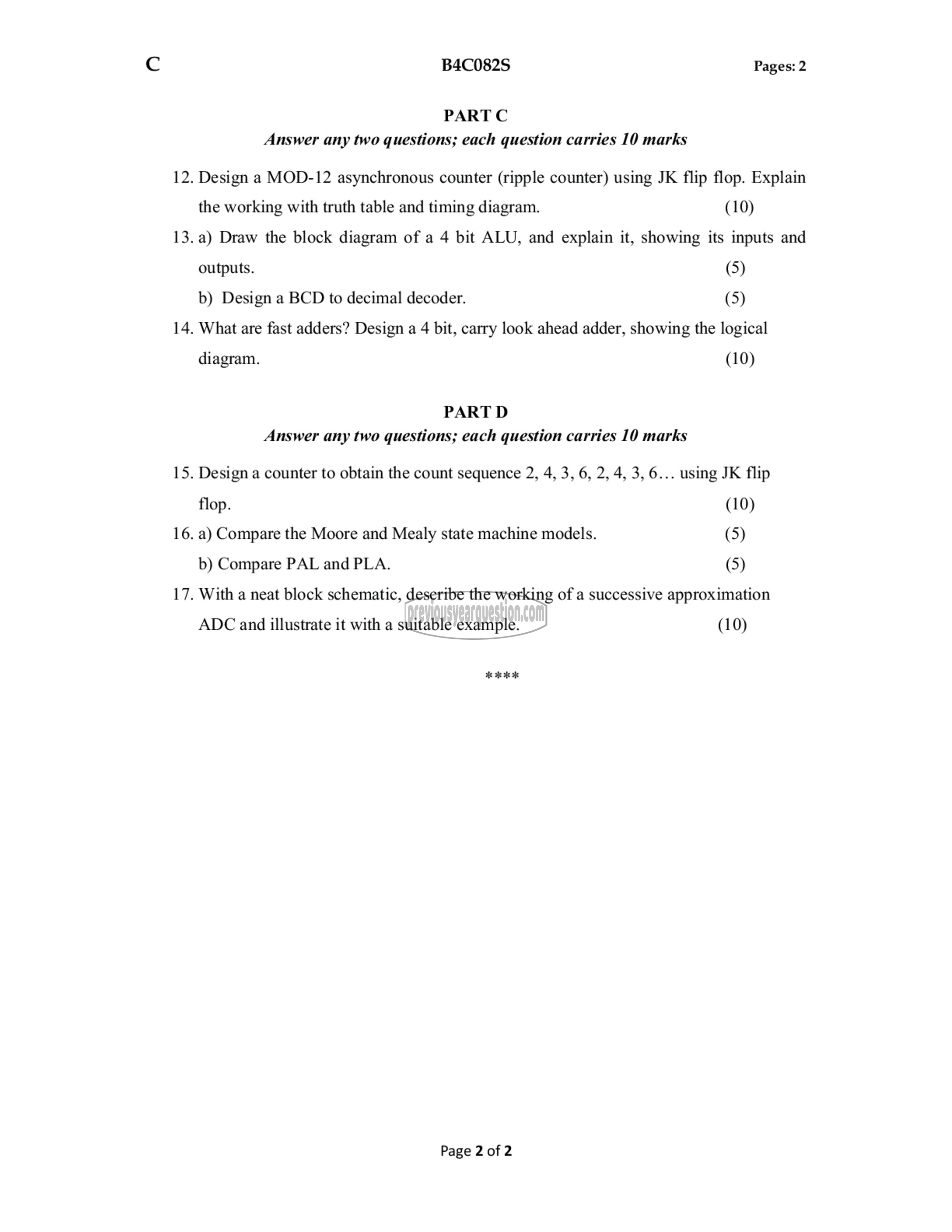

PART C

Answer any two questions; each question carries 10 marks

. Design a MOD-12 asynchronous counter (ripple counter) using JK flip flop. Explain

the working with truth table and timing diagram. (10)

. 8) Draw the block diagram of a 4 bit ALU, and explain it, showing its inputs and

outputs. (5)

b) Design a BCD to decimal decoder. (5)

. What are fast adders? Design a 4 bit, carry look ahead adder, showing the logical

diagram. (10)

PART 0

Answer any two questions; each question carries 10 marks

. Design a counter to obtain the count sequence 2, 4, 3, 6, 2, 4, 3, 6... using JK flip

flop. (10)

. a) Compare the Moore and Mealy state machine models. (5)

b) Compare PAL and PLA. (5)

. With a neat block schematic, describe the working of a successive approximation

ADC and illustrate it with a suitable example. (10)

ie a بد باد

Page 2 of 2