APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 5

Subject : VLSI Circuit Design

Year : 2020

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : AE 363

Page:1

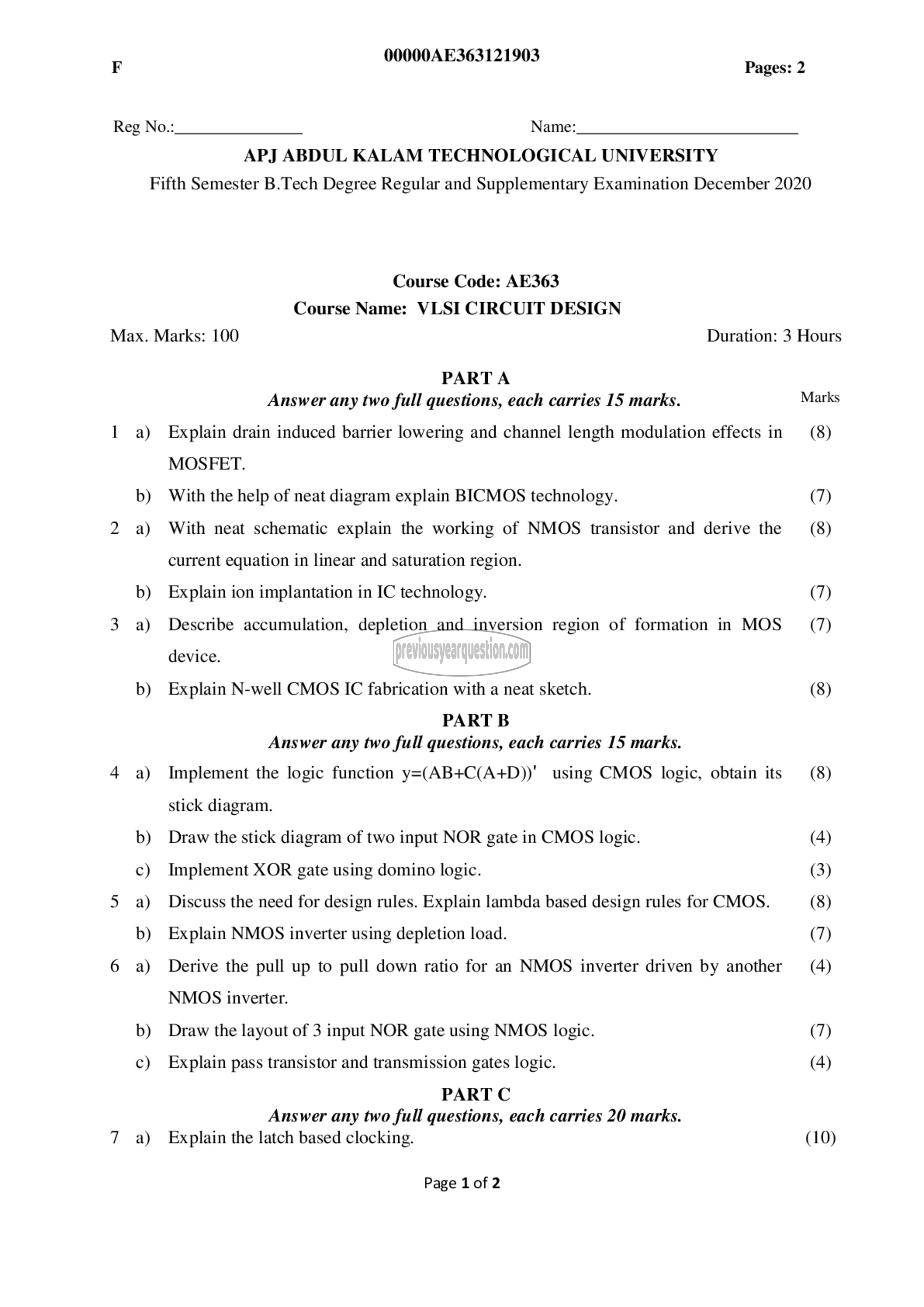

00000AE363121903 Pages: 2

Reg No.: Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

Fifth Semester B.Tech Degree Regular and Supplementary Examination December 2020

Course Code: AE363

Course Name: VLSI CIRCUIT DESIGN

Max. Marks: 100 Duration: 3 Hours

PARTA

Answer any two full questions, each carries 15 marks. Marks

1 a) Explain drain induced barrier lowering and channel length modulation effects in (8)

MOSFET.

b) With the help of neat diagram explain BICMOS technology. (7)

2 a) With neat schematic explain the working of NMOS transistor and derive the (8)

current equation in linear and saturation region.

b) Explain ion implantation in IC technology. (7)

3 a) Describe accumulation, depletion and inversion region of formation in MOS (7)

device.

b) Explain N-well CMOS IC fabrication with a neat sketch. (8)

PART تا

Answer any two full questions, each carries 15 marks.

4 a) Implement the logic function y=(AB+C(A+D))' using CMOS logic, obtain its (8)

stick diagram.

b) Draw the stick diagram of two input NOR gate in CMOS logic. (4)

c) Implement XOR gate using domino logic. (3)

5 a) Discuss the need for design rules. Explain lambda based design rules for CMOS. (8)

b) Explain NMOS inverter using depletion load. (7)

6 a) Derive the pull up to pull down ratio for an NMOS inverter driven by another (4)

NMOS inverter.

b) Draw the layout of 3 input NOR gate using NMOS logic. (7)

c) Explain pass transistor and transmission gates logic. (4)

PART C

Answer any two full questions, each carries 20 marks.

7 a) Explain the latch based clocking. (10)

Page 1 of 2