APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

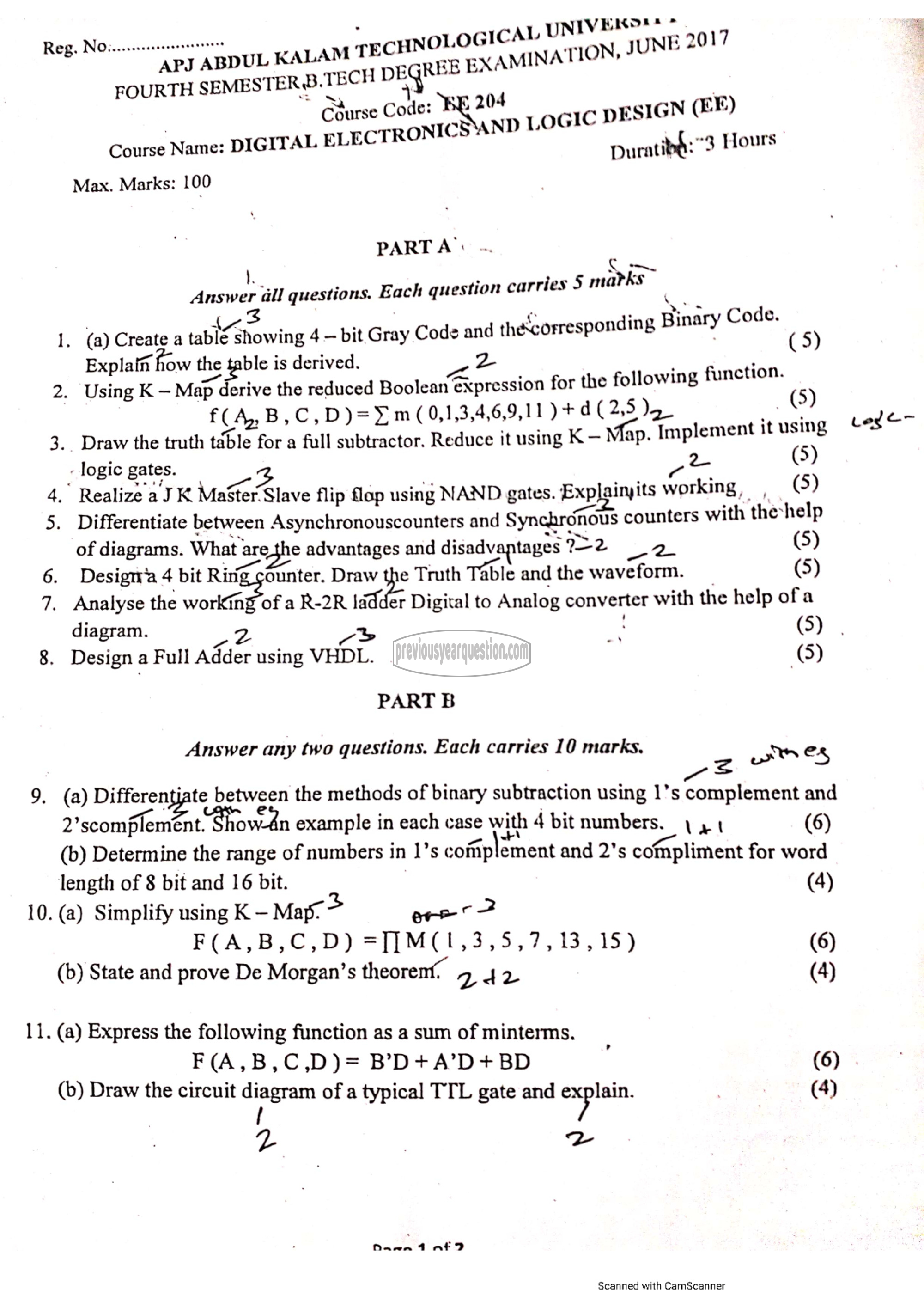

Semester : SEMESTER 4

Subject : Digital Electronics and Logic Design

Year : 2017

Term : JUNE

Scheme : 2015 Full Time

Course Code : EE 204

Page:1

ICAL UNIVEKO#* 7 -

E 1 G 5 1 © ۱ءء

Reg. No.....- APJ ABDUL KALAM 1४०8 EXAMINATION: JUNE

دنا TE TECH DE ೨೭

FOURTH SEMES TERS.) ட இ |

Course Code: 243 204 9 pESIGN (00)

+ 2)

⋅ 5 ELECTRONICSAND 14

Course Name: DIGITAL tLECTR ۹ء0 Hours

Max. Marks: 100

- الى و ہی

५ ~

rries 5 marks

۱

ತ್್

g Binary Code.

Answer all questions. Each question ca

1. (a) Create a ಜ್ 4—bit Gray Code and thecorrespondin (5)

Explain how the table is derived. ہے त ∙≂⋅

∑∙⋃≘⇂⋅⊓⊑↧≺−− Map derive the reduced Boolean expression for the following function. 5

f(A, B,C,D)=¥m(0,1,3,4,6,9,11) + 0 ) 2,5 ہے لی = ے(

3. Draw the truth table for a full subtractor. Reduce it using کل - ۷ fap. Implement it using

‘logic gates. — 3 2 (5)

4," Realize'a J 1> MaSter Slave flip flap using NAND gates. Explginits working, । (5)

5. Differentiate between Asynchronouscounters and Synchronous counters with ند

of diagrams. What are the advantages and disadvantages Io. 2

൫ ^ 5 = न ತ ٠ Tab کے 5

6. 106519755 4 bit Ring counter. Draw ue Truth Table and the waveform. =. (5)

7, Analyse the working of a R-2R ladder Digital to Analog converter with the help ofa

(൭

diagram. Py کے 0

8. Design a Full Adder using VHDL. (5)

PART B

Answer any two questions. Each carries 10 marks. 5 س٠ ९९

tween the methods of binary subtraction using 1' 5 complement and

9. (a) سين ௮ be

9 > گے 71 ⋅ ∙ ⋅∙

∑⋮∘∘⋯↥⊃∣∁⋯⊜⊓↥⋅ “Show-4n example in each case with 4 bit numbers. (ച (6)

(0) Determine the range of numbers in 1'5 complement and 25 compliment for word

length of 8 bit and 16 bit. (4)

10. (a) Simplify using K - كرو ere?

F(A,B,C,D) =[][M(l,3,5,7,13,15) (6)

(b) State and prove De Morgan’s theorent 2, 4 2- (4)

11. (a) Express the following function as a sum of minterms.

F(A,B,C,D)= BD+A’D+BD (6)

(b) Draw the circuit diagram of a typical TTL gate and का बहआ ↼ (4)

س2

2

9و و ಣಾ

Scanned with CamScanner