APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 4

Subject : Digital Electronics and Logic Design

Year : 2017

Term : JUNE

Scheme : 2015 Full Time

Course Code : EE 204

Page:2

0 B4C081 ∙ Pages; 2

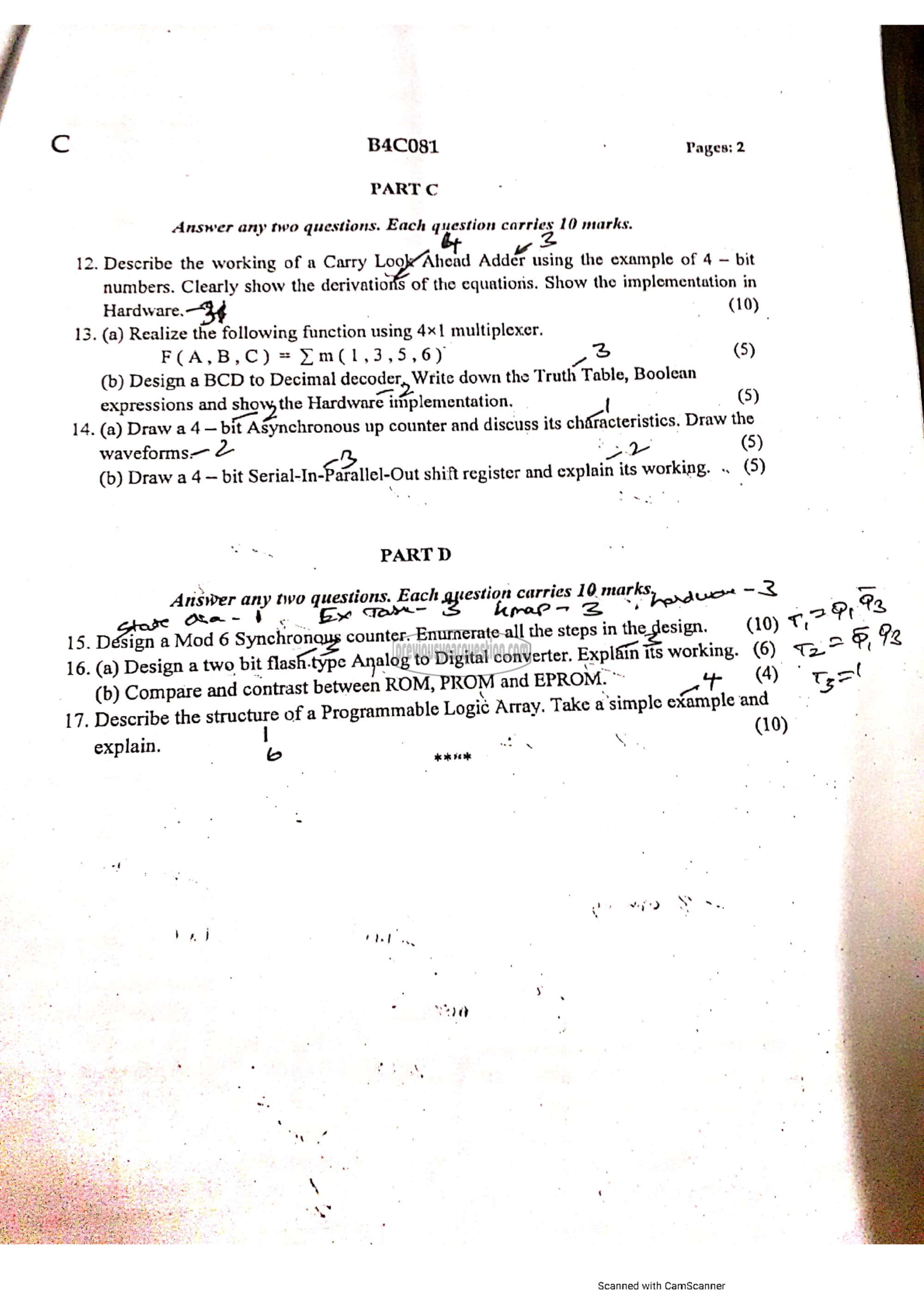

PART ©

Answer any two questions. Each question carries 10 marks.

۱ by

12. Describe the working of a Carry ee ദോ using the example of 4 - bit

numbers. Clearly show the derivatiorfs of the equations. Show the implementation in

Hardware. (10)

13. (a) Realize the following function using 4×1 multiplexer. ۱ ۱

F(A,B,C) = }m(1,3,5,6) 2 (5)

(b) Design a BCD to Decimal decoder, Write down the Truth Table, Boolean

expressions and show, the Hardware itnplementation , ७)

14. (a) Draw ೩ 4 - bit ASynchronous up counter and discuss its chfracteristics. Draw the

waveforms— Lye (5)

(ए) Draw a 4 — bit Serial-In Parallel-Out shift register and explain its working (5)

` ل PART D

Answer any two questions. Each gpestion ೦177105 10 mar. wo -2 —

Ora - ‘a 4, TOs لا freer ree तह के 3ھ“

(

15.0 28 a Mod 6 Synchronaus counter. Enumerate all the steps in the design

16. (a) Design a two bit +8768 An alog to Digital converter Explain its working. (6) Ta

(b) Compare and contrast between ROM, PROM and EPROM Pas ५८ ` क, ہے

17. Describe the structure of a Programmable Logic Array Take a’simple example an

∙ ∣ ⋅ ∖ (10

explain. ۱ 7 cam ಗೆ ಯ

0 Hey wos

“ae

Scanned with CamScanner