APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 5

Subject : Digital System Design

Year : 2020

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EE 365

Page:1

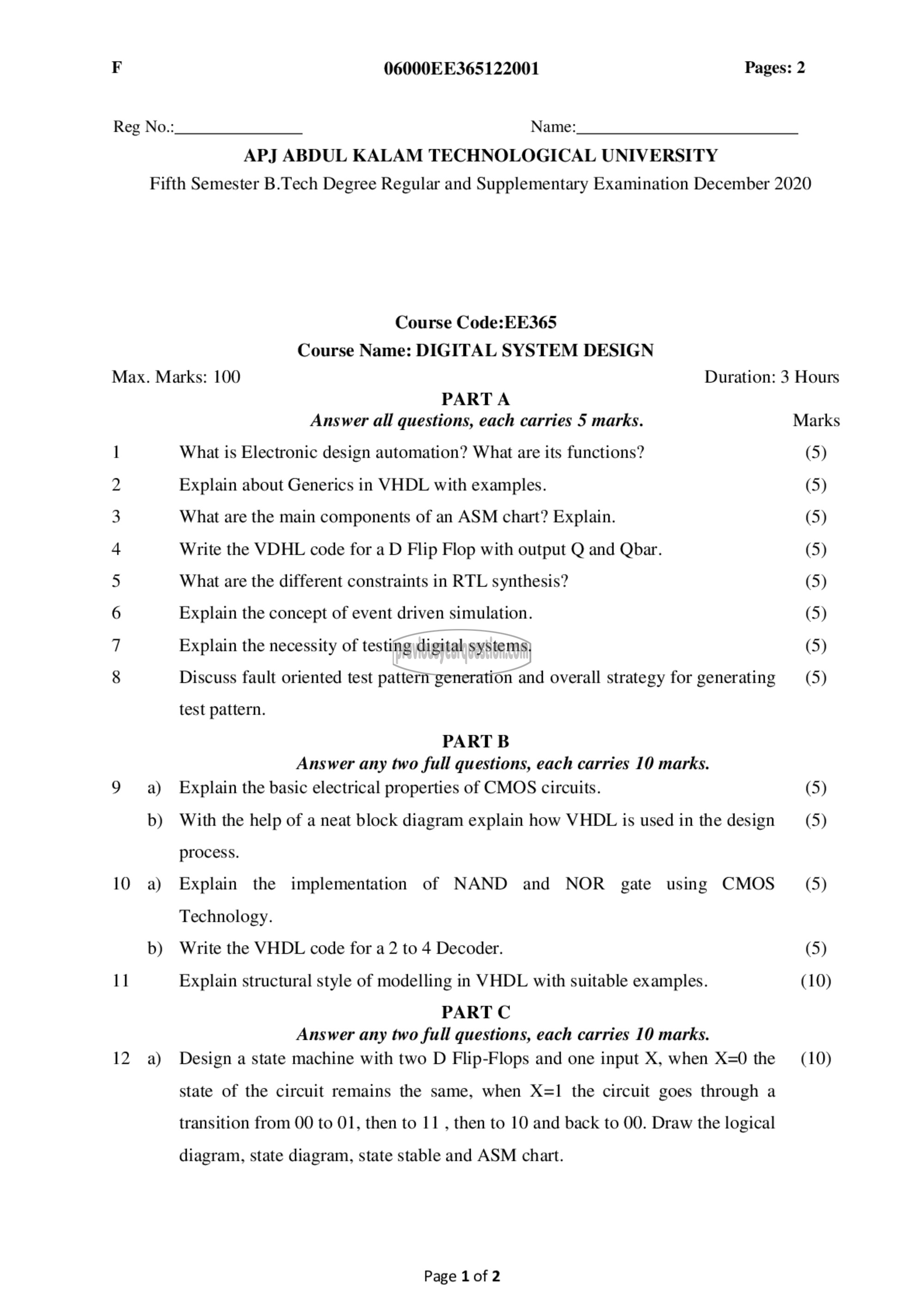

F 06000EE365122001 Pages: 2

Reg No.: Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

Fifth Semester B.Tech Degree Regular and Supplementary Examination December 2020

Course Code: EE365

Course Name: DIGITAL SYSTEM DESIGN

Max. Marks: 100 Duration: 3 Hours

PARTA

Answer all questions, each carries 5 marks. Marks

1 What is Electronic design automation? What are its functions? (5)

2 Explain about Generics in VHDL with examples. (5)

3 What are the main components of an ASM chart? Explain. (5)

4 Write the VDHL code for a D Flip Flop with output Q and Qbar. (5)

5 What are the different constraints in RTL synthesis? (5)

6 Explain the concept of event driven simulation. (5)

7 Explain the necessity of testing digital systems. (5)

8 Discuss fault oriented test pattern generation and overall strategy for generating (5)

test pattern.

PART 13

Answer any two full questions, each carries 10 marks.

9 ച Explain the basic electrical properties of CMOS circuits. (5)

b) With the help of a neat block diagram explain how VHDL is used in the design (5)

process.

10 a) Explain the implementation of NAND and NOR gate using CMOS (5)

Technology.

b) Write the VHDL code for a 2 to 4 Decoder. (5)

11 Explain structural style of modelling in VHDL with suitable examples. (10)

PART C

Answer any two full questions, each carries 10 marks.

12 a) Design ೩ state machine with two D Flip-Flops and one input X, when X=0 the (10)

state of the circuit remains the same, when >=] the circuit goes through a

transition from 00 to 01, then to 11 , then to 10 and back to 00. Draw the logical

diagram, state diagram, state stable and ASM chart.

Page 1 of 2