APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : LOGIC CIRCUIT DESIGN

Year : 2020

Term : DECEMBER

Scheme : 2019 Full Time

Course Code : ECT 203

Page:2

20

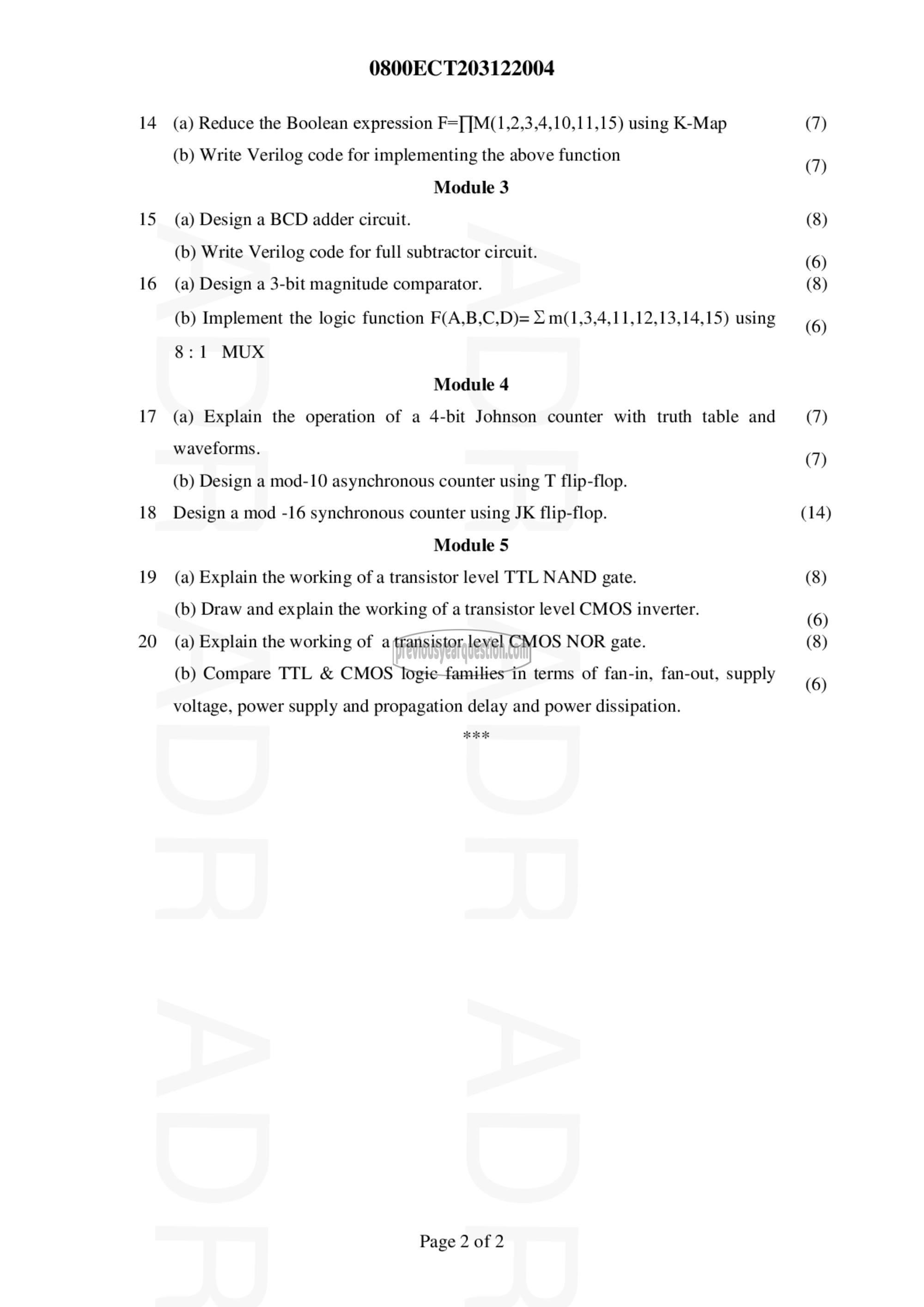

0800ECT203122004

(a) Reduce the Boolean expression F=[]TM(1,2,3,4,10,11,15) using K-Map

(b) Write Verilog code for implementing the above function

Module 3

(a) Design a BCD adder circuit.

(b) Write Verilog code for full subtractor circuit.

(a) Design a 3-bit magnitude comparator.

(0) Implement the logic function F(A,B,C,D)= © m(1,3,4,11,12,13,14,15) using

8:1 MUX

Module 4

(a) Explain the operation of a 4-bit Johnson counter with truth table and

waveforms.

(b) Design a mod-10 asynchronous counter using T flip-flop.

Design a mod -16 synchronous counter using JK flip-flop.

Module 5

(a) Explain the working of a transistor level TTL NAND gate.

(b) Draw and explain the working of a transistor level CMOS inverter.

(a) Explain the working of a transistor level CMOS NOR gate.

(b) Compare TTL & CMOS logic families in terms of fan-in, fan-out, supply

voltage, power supply and propagation delay and power dissipation.

Page 2 of 2

(7)

(7)

(8)

(6)

(8)

(6)

(7)

(7)

(14)

(8)

(6)

(8)

(6)