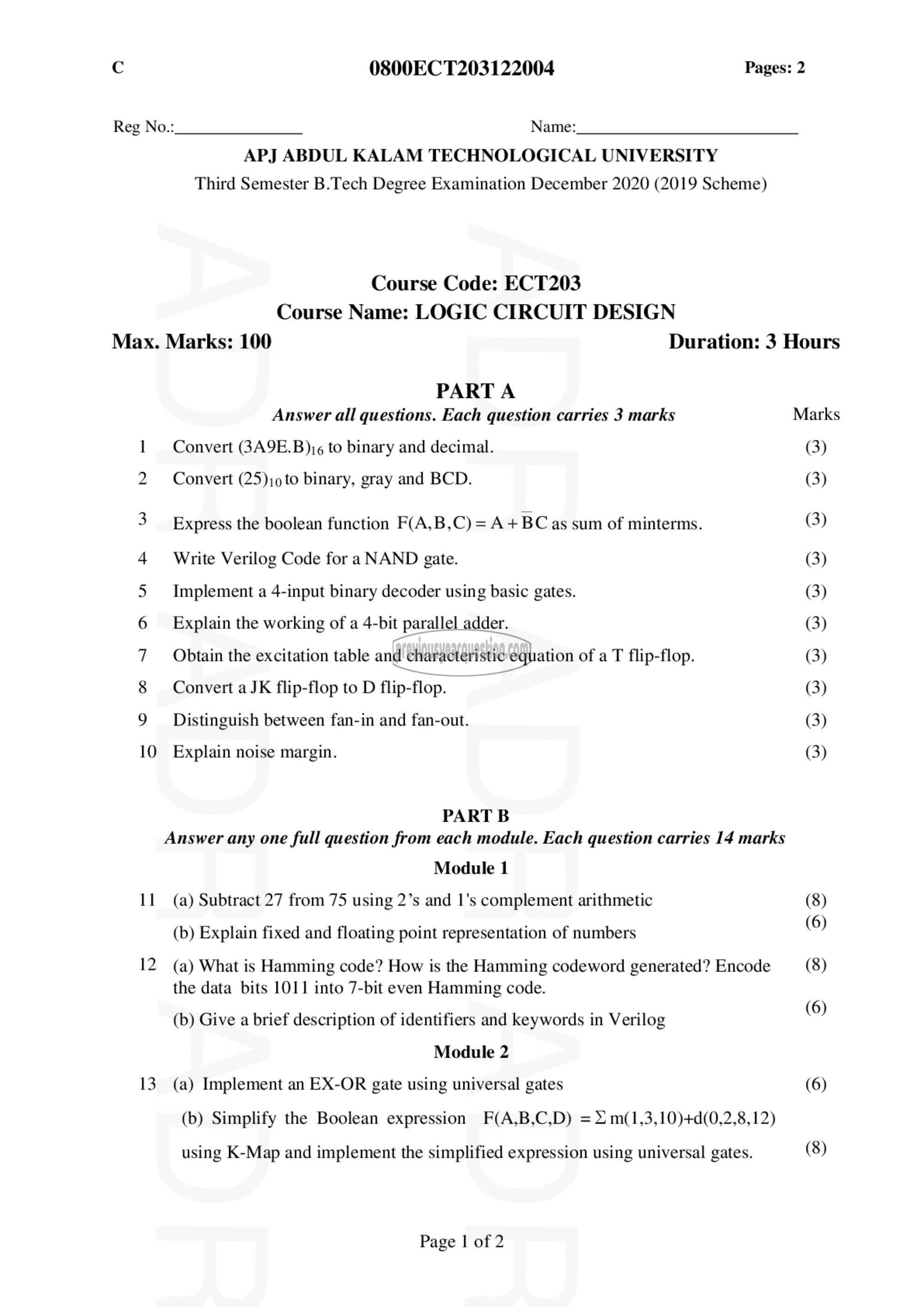

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : LOGIC CIRCUIT DESIGN

Year : 2020

Term : DECEMBER

Scheme : 2019 Full Time

Course Code : ECT 203

Page:1

0800ECT203122004 Pages: 2

Reg No.: Name:

Max. Marks: 100

11

12

13

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

Third Semester B.Tech Degree Examination December 2020 (2019 Scheme)

Course Code: ECT203

Course Name: LOGIC CIRCUIT DESIGN

PARTA

Answer all questions. Each question carries 3 marks

Convert (3A9E.B)j6 to binary and decimal.

Convert (25010 binary, gray and BCD.

Express the boolean function F(A,B,C) = ^ + BC as sum of minterms.

Write Verilog Code fora NAND gate.

Implement a 4-input binary decoder using basic gates.

Explain the working of a 4-bit parallel adder.

Obtain the excitation table and characteristic equation of a T flip-flop.

Convert a JK flip-flop to D flip-flop.

Distinguish between fan-in and fan-out.

Explain noise margin.

PART 13

Answer any one full question from each module. Each question carries 14 marks

Module 1

(a) Subtract 27 from 75 using 2’s and 1's complement arithmetic

(b) Explain fixed and floating point representation of numbers

(a) What is Hamming code? How is the Hamming codeword generated? Encode

the data bits 1011 into 7-bit even Hamming code.

(b) Give a brief description of identifiers and keywords in Verilog

Module 2

(a) Implement an EX-OR gate using universal gates

(0) Simplify the Boolean expression F(A,B,C,D) = > m(1,3,10)+d(0,2,8,12)

using K-Map and implement the simplified expression using universal gates.

Page | of 2

Duration: 3 Hours

Marks

(3)

(3)

(3)

(3)

(3)

(3)

(3)

(3)

(3)

(3)

(8)

(6)

(8)

(6)

(6)

(8)