APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 7

Subject : Computer System Architecture

Year : 2019

Term : DECEMBER

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 405

Page:3

16

17

18

19

a)

b)

0)

a)

b)

a)

b)

a)

b)

G192056 Pages:3

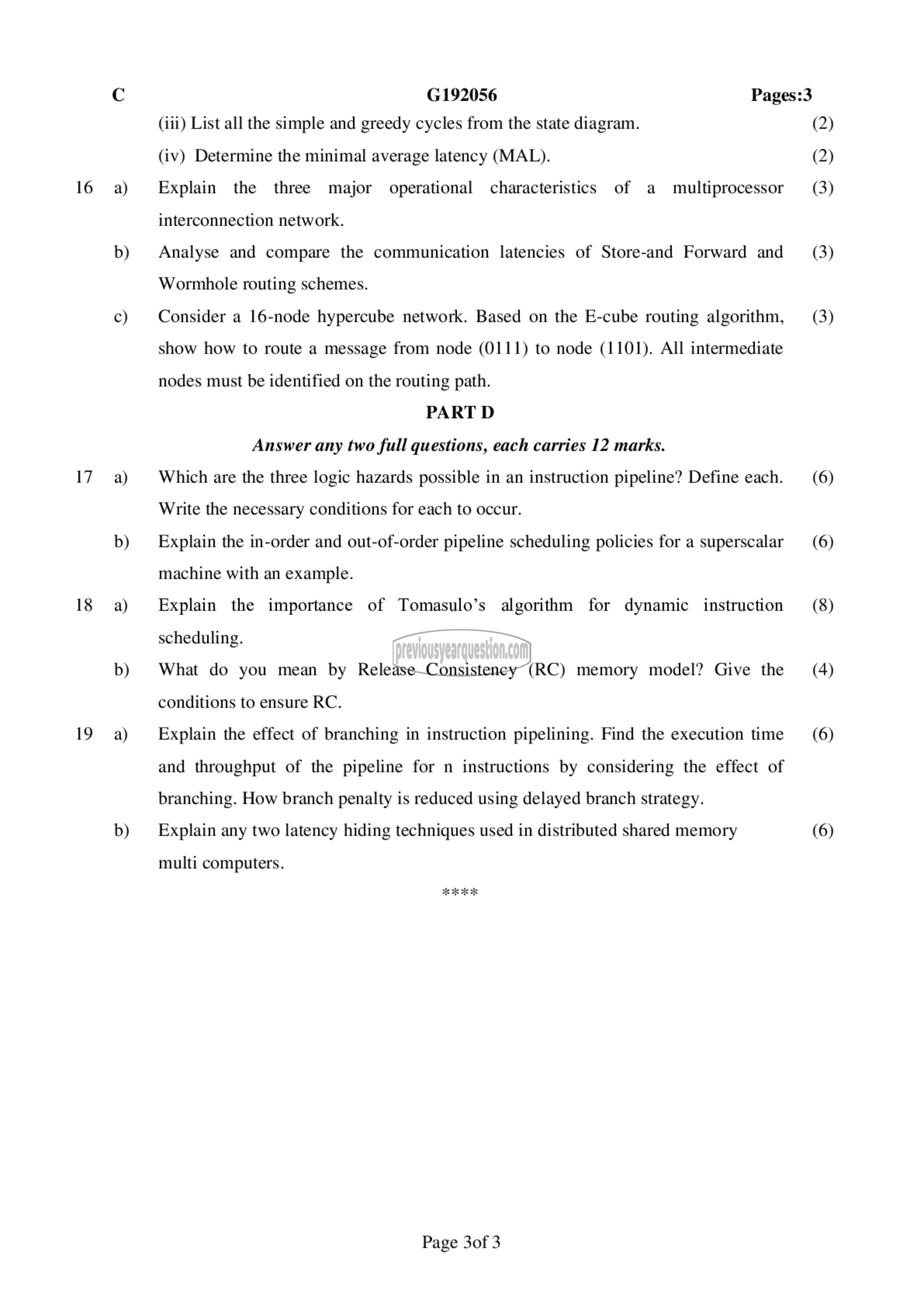

(111) List all the simple and greedy cycles from the state diagram.

(iv) Determine the minimal average latency (MAL).

Explain the three major operational characteristics of a multiprocessor

interconnection network.

Analyse and compare the communication latencies of Store-and Forward and

Wormhole routing schemes.

Consider a 16-node hypercube network. Based on the E-cube routing algorithm,

show how to route a message from node (0111) to node (1101). All intermediate

nodes must be identified on the routing path.

PART D

Answer any two full questions, each carries 12 marks.

Which are the three logic hazards possible in an instruction pipeline? Define each.

Write the necessary conditions for each to occur.

Explain the in-order and out-of-order pipeline scheduling policies for a superscalar

machine with an example.

Explain the importance of Tomasulo’s algorithm for dynamic instruction

scheduling.

What do you mean by Release Consistency (RC) memory model? Give the

conditions to ensure RC.

Explain the effect of branching in instruction pipelining. Find the execution time

and throughput of the pipeline for n instructions by considering the effect of

branching. How branch penalty is reduced using delayed branch strategy.

Explain any two latency hiding techniques used in distributed shared memory

multi computers.

॥

Page 3of 3

(2)

(2)

(3)

(3)

(3)

(6)

(6)

(8)

(4)

(6)

(6)