APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Logic Circuit Design

Year : 2022

Term : JANUARY

Scheme : 2015 Full Time

Course Code : EC 207

Page:2

b)

a)

b)

a)

00000EC207121901

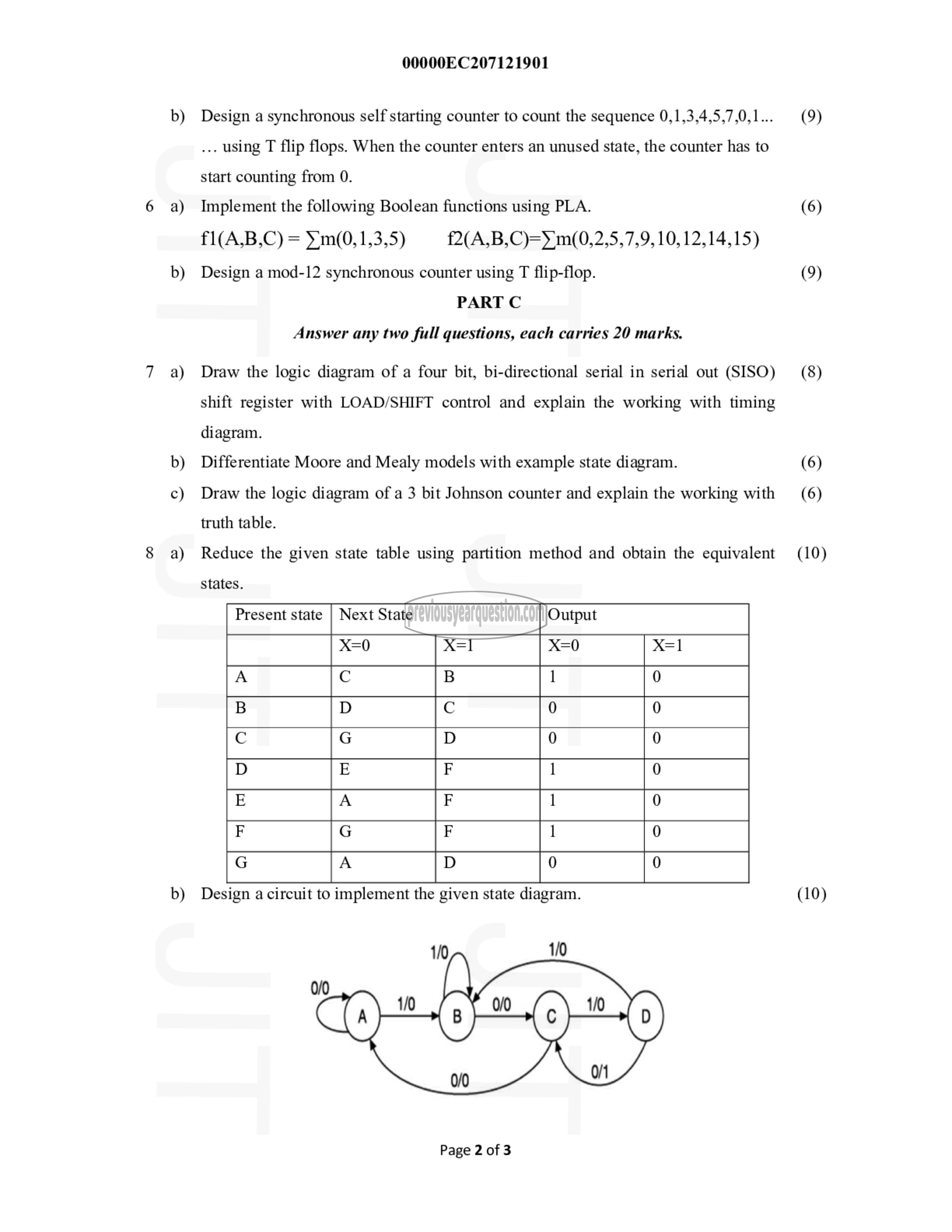

Design a synchronous self starting counter to count the sequence 0,1,3,4,5,7,0,1...

... using T flip flops. When the counter enters an unused state, the counter has to

start counting from 0.

Implement the following Boolean functions using PLA.

f1(A,B,C) = 3:00, 1,3,5) f2(A,B,C)=)'m(0,2,5,7,9, 10,12,14,15)

Design a mod-12 synchronous counter using T flip-flop.

PART ^

Answer any two full questions, each carries 20 marks.

Draw the logic diagram of a four bit, bi-directional serial in serial out (SISO)

shift register with LOAD/SHIFT control and explain the working with timing

diagram.

Differentiate Moore and Mealy models with example state diagram.

Draw the logic diagram of a 3 bit Johnson counter and explain the working with

truth table.

Reduce the given state table using partition method and obtain the equivalent

states.

Present state | Next State Output

Page 2 of 3

(9)

(6)

(9)

(8)

(6)

(6)

(10)

(10)