APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

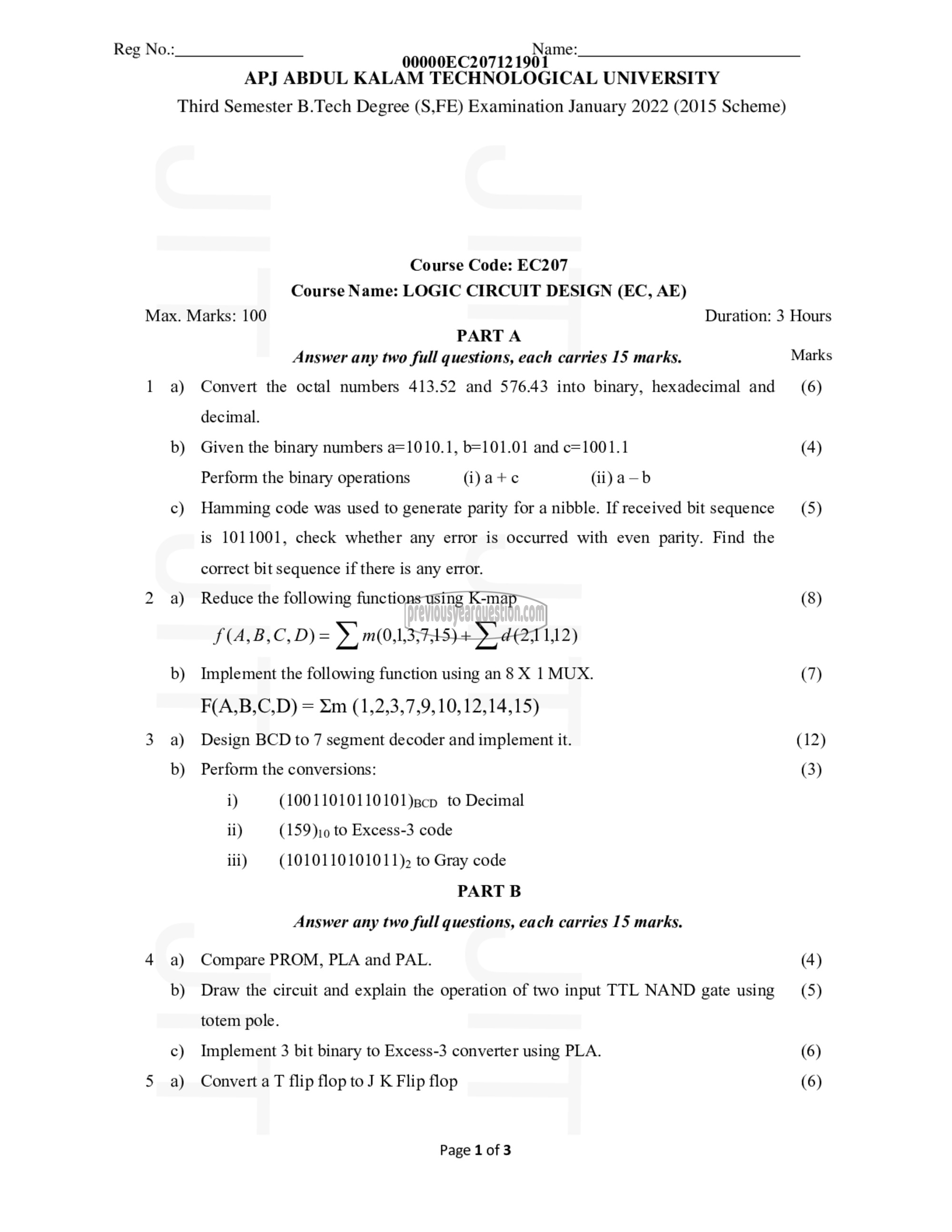

Semester : SEMESTER 3

Subject : Logic Circuit Design

Year : 2022

Term : JANUARY

Scheme : 2015 Full Time

Course Code : EC 207

Page:1

Reg No.:

Max. Marks: 100

ا۲

Third Semester B.Tech Degree (S,FE) Examination January 2022 (2015 Scheme)

a)

b)

९)

2)

b)

a)

b)

a)

b)

०)

8)

000000८2072191

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

Course Code: EC207

Course Name: LOGIC CIRCUIT DESIGN (EC, AE)

PART A

Answer any two full questions, each carries 15 marks.

Convert the octal numbers 413.52 and 576.43 into binary, hexadecimal and

decimal.

Given the binary numbers a=1010.1, b=101.01 and c=1001.1

Perform the binary operations (ijate (ii) 8 - 9

Hamming code was used to generate parity for a nibble. If received bit sequence

is 1011001, check whether any error is occurred with even parity. Find the

correct bit sequence if there is any error.

Reduce the following functions using K-map

f (A,B,C, 0) = 2_ m(0,1,3,7,15) + 2_ d(2,1 1,12)

Implement the following function using an 8 X 1 MUX.

F(A,B,C,D) = =m (1,2,3,7,9, 10,12,14,15)

Design BCD to 7 segment decoder and implement it.

Perform the conversions:

i) (10011010110101)8त to Decimal

ii) (159); to Excess-3 code

iii) (1010110101011), to Gray code

PART تا

Answer any two full questions, each carries 15 marks.

Compare PROM, PLA and PAL.

Draw the circuit and explain the operation of two input TTL NAND gate using

totem pole.

Implement 3 bit binary to Excess-3 converter using PLA.

Convert a T flip flop to J K Flip flop

Page 1 of 3

Duration: 3 Hours

Marks

(6)

(4)

(5)

(8)

(4)

(5)

(6)

(6)