APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 5

Subject : Digital System Design

Year : 2017

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EC 361

Page:1

F7196

Total Pages: 3

Reg No.: Name:

Max. Marks: 100

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

FIFTH SEMESTER B.TECH DEGREE EXAMINATION, DECEMBER 2017

Course Code: EC361

Course Name: DIGITAL SYSTEM DESIGN (EC, AE)

Duration: 3 Hours

PART A

Answer any two full questions, each carries 15 marks. Marks

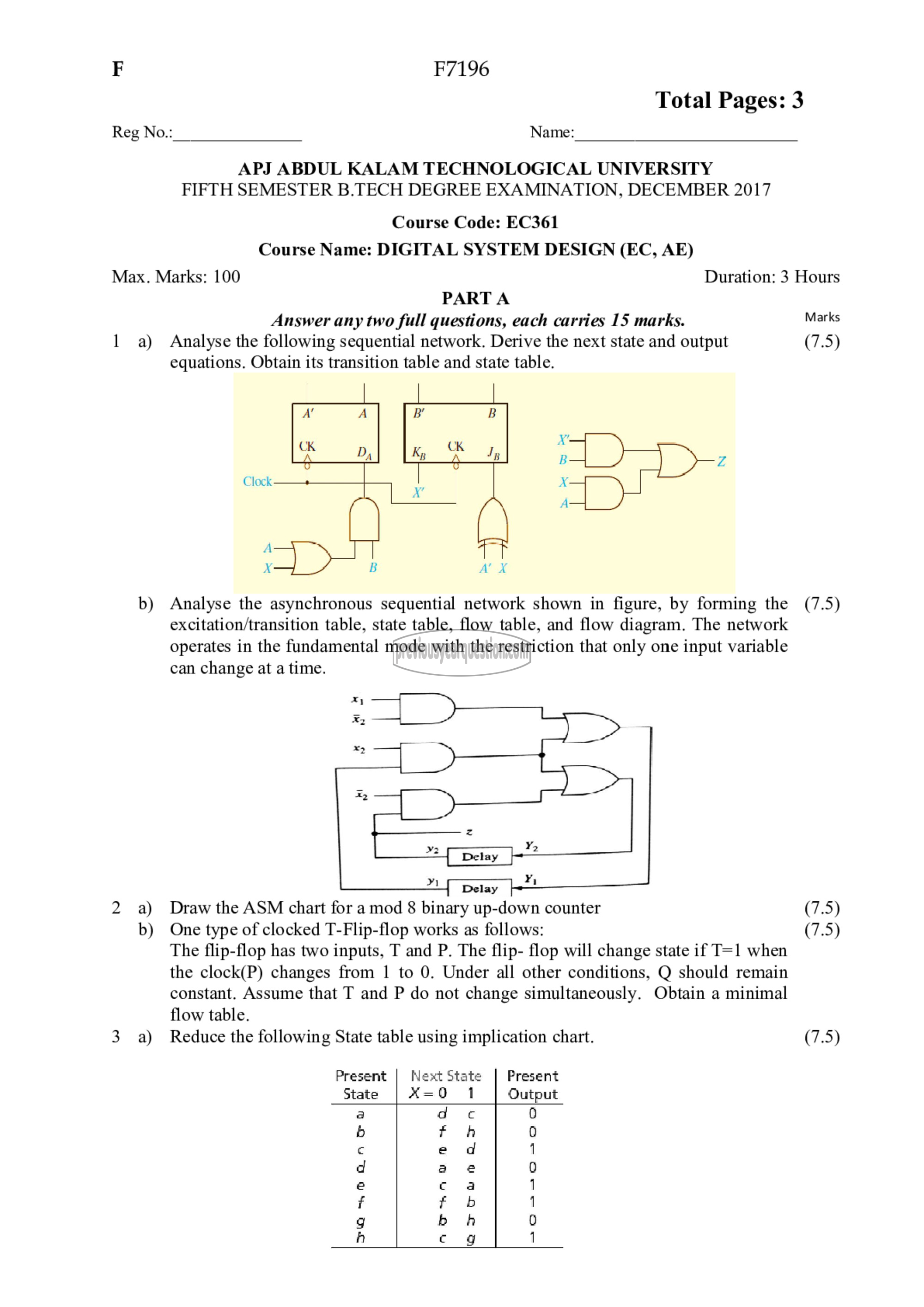

1 a) Analyse the following sequential network. Derive the next state and output (7.5)

equations. Obtain its transition table and state table.

പ ہے

mo ० bY

N

b) Analyse the asynchronous sequential network shown in figure, by forming the (7.5)

2 a)

b)

3 ஐ

excitation/transition table, state table, flow table, and flow diagram. The network

operates in the fundamental mode with the restriction that only one input variable

can change at a time.

Draw the ASM chart for a mod 8 binary up-down counter (7.5)

One type of clocked T-Flip-flop works as follows: (7.5)

The flip-flop has two inputs, T and P. The flip- flop will change state if T=1 when

the clock(P) changes from | to 0. Under all other conditions, Q should remain

constant. Assume that T and P do not change simultaneously. Obtain a minimal

flow table.

Reduce the following State table using implication chart. (7.5)

Present | Next State | Present

State | X= 1 Output

0

८0 1 | 0 +~ مهو ^+ عه م