APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Logic Circuit Design

Year : 2020

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EC 207

Page:2

a)

b)

a)

b)

a)

b)

00000EC20712 1903

PART ^

Answer any two full questions, each carries 20 marks.

Construct a 4 bit serial-in serial-out 10/1 shift register using JK FF. Describe its

operation on every clock pulse.

Show the state table and Mealy model state diagram of JK FF. Derive its

characteristic equation

Design a 3-bit asynchronous up/down counter using JK FF that counts up when

the mode M=1 and counts down when Mode=0. How does the circuit work

Explain the working of a twisted ring counter, with the help of timing diagrams.

Design a circuit to detect the sequence 1010 with overlapping, using D FF. Draw

the state diagram, state table, excitation table and the circuit

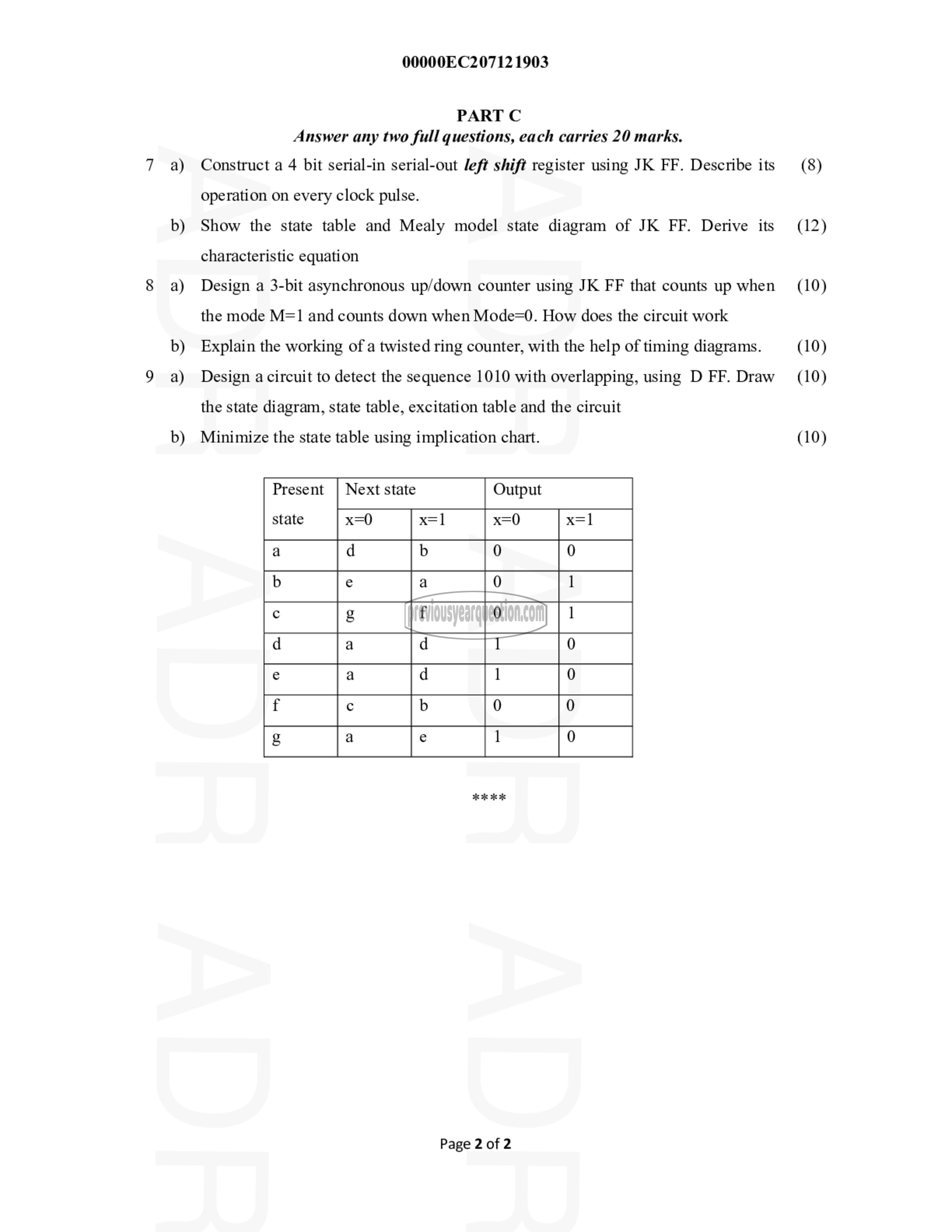

Minimize the state table using implication chart.

Present | Next state Output

state

ok ok

Page 2 of 2

(8)

(12)

(10)

(10)

(10)

(10)