APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Logic Circuit Design

Year : 2020

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EC 207

Page:1

Reg No.: 7 Name:

00000EC207121903

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

Third Semester B.Tech Degree (S,FE) Examination December 2020 (2015 Scheme)

Course Code: EC207

Course Name: LOGIC CIRCUIT DESIGN (EC, AE)

Max. Marks: 100 Duration: 3 Hours

PART A

Answer any two full questions, each carries 15 marks. Marks

1 a) Convert the decimal number 963 to its equivalent Octal, Hexadecimal, BCD, (10)

Gray, XS-3 codes.

b) Determine the Hamming code for the information 1101, with even parity. (5)

2 8) Simplify using K-map F(a,b,c,d) = ൮൩ (3,7,11,13,15} Yd (0,12,14) and (10)

implement the circuit using NAND gates.

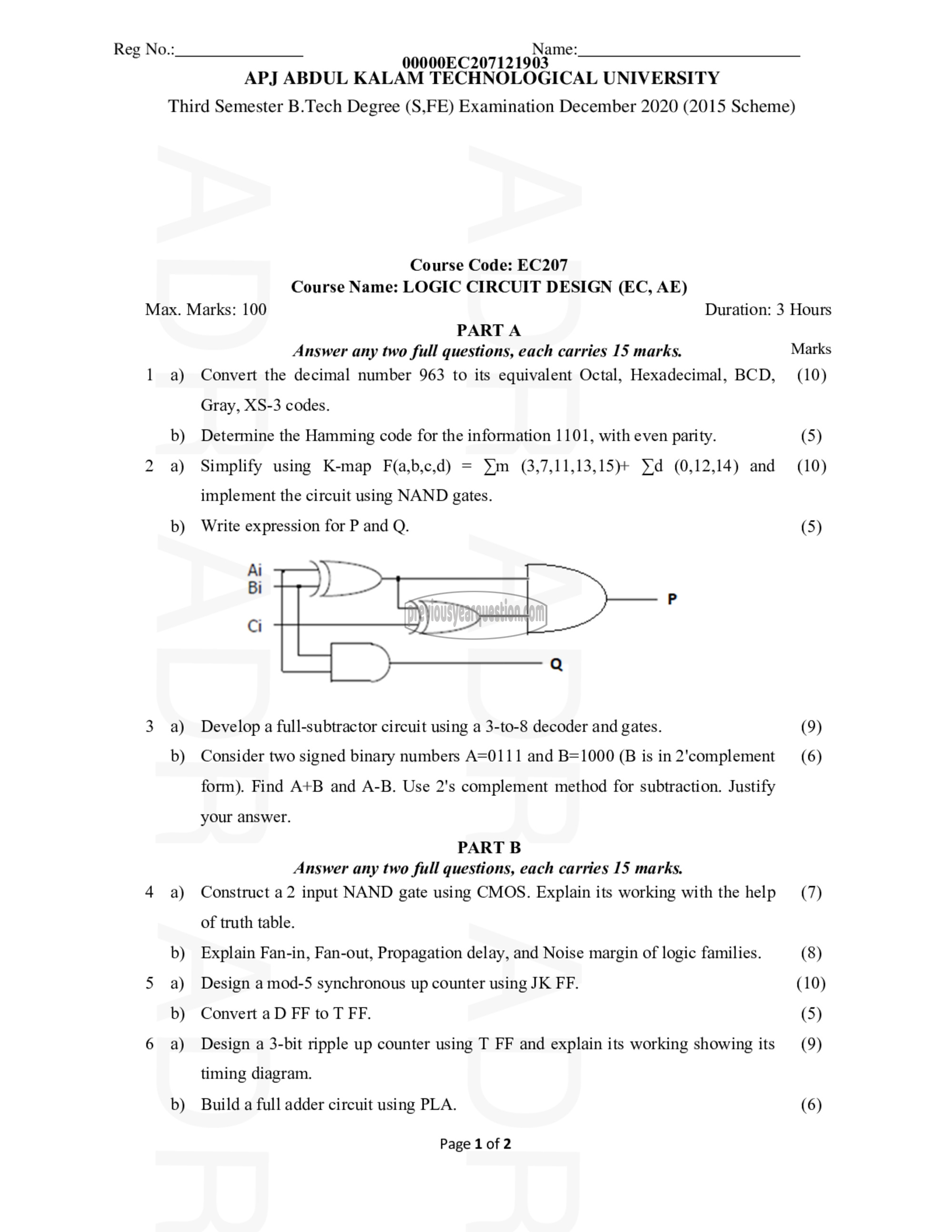

b) Write expression for P and Q. (5)

Ai ತ್ಾ ہر سام

ಜತ.

ಬ ۲

ಆ 71997

Q

3 a) Develop a full-subtractor circuit using a 3-10-8 decoder and gates. (9)

b) Consider two signed binary numbers A=0111 and B=1000 (B is in2'complement (6)

form). Find A+B and A-B. Use 2's complement method for subtraction. Justify

your answer.

PART تا

Answer any two full questions, each carries 15 marks.

4 a) Construct a2 input NAND gate using CMOS. Explain its working with the help (7)

of truth table.

b) Explain Fan-in, Fan-out, Propagation delay, and Noise margin of logic families. (8)

5 8) Design a mod-5 synchronous up counter using JK FF. (10)

b) Convert a D FF to T FF (5)

6 a) Design a 3-bit ripple up counter using 1 FF and explain its working showing its (9)

timing diagram.

b) Build a full adder circuit using PLA. (6)

Page 1 of 2