APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 5

Subject : Digital System Design

Year : 2020

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EC 361

Page:2

06000EC361122003

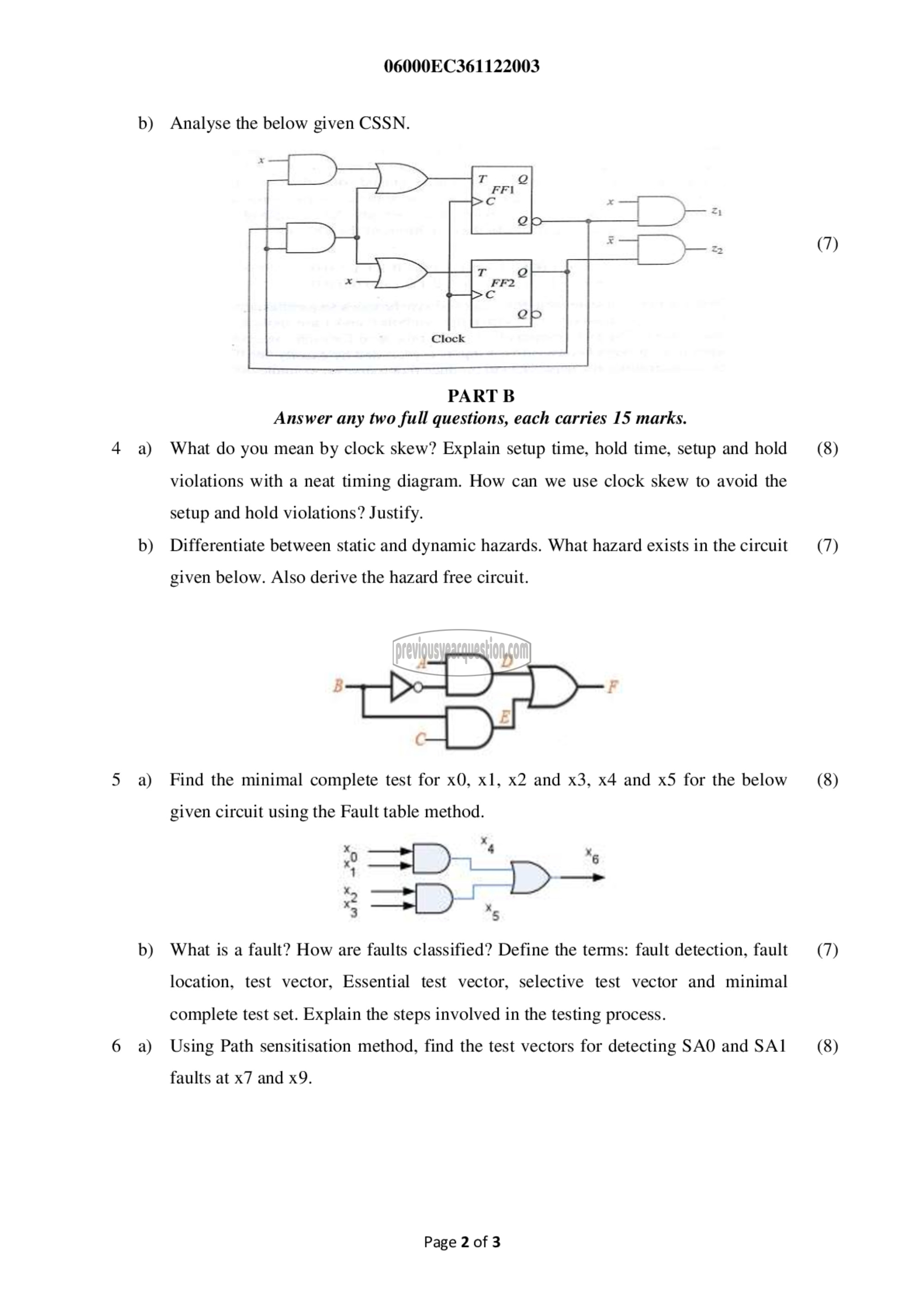

b) Analyse the below given CSSN.

(7)

PART 13

Answer any two full questions, each carries 15 marks.

a) What do you mean by clock skew? Explain setup time, hold time, setup and hold (8)

violations with a neat timing diagram. How can we use clock skew to avoid the

setup and hold violations? Justify.

b) Differentiate between static and dynamic hazards. What hazard exists in the circuit (7)

given below. Also derive the hazard free circuit.

a) Find the minimal complete test for x0, ೫1, x2 and x3, x4 and x5 for the below (8)

given circuit using the Fault table method.

b) What is a fault? How are faults classified? Define the terms: fault detection, fault (7)

location, test vector, Essential test vector, selective test vector and minimal

complete test set. Explain the steps involved in the testing process.

a) Using Path sensitisation method, find the test vectors for detecting SAO and SAI (8)

faults at x7 and x9.

Page 2 of 3