APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Switching Theory and Logic Design

Year : 2019

Term : MAY

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 203

Page:3

15

16

17

18

19

20

a)

b)

0)

a)

b)

C1120 Pages: 3

PART E

Answer any four full questions, each carries10 marks.

With the help of a neat diagram discuss how a serial adder can be designed using (10)

full-adder, shift registers and flip-flop.

Design a synchronous counter, using edge-triggered J-K flip-flops, that generates (10)

the binary sequence: 001, 011, 010, 110, 111, 101, 001, 000, 001, ...

Draw a mod-16 ripple up-counter using J-Kflip-flops. Show how this counter can (10)

be converted to a mod-12 ripple counter.

How is static RAM different from dynamic RAM? (3)

Write explanatory notes on read-only memory and read-write memory. (4)

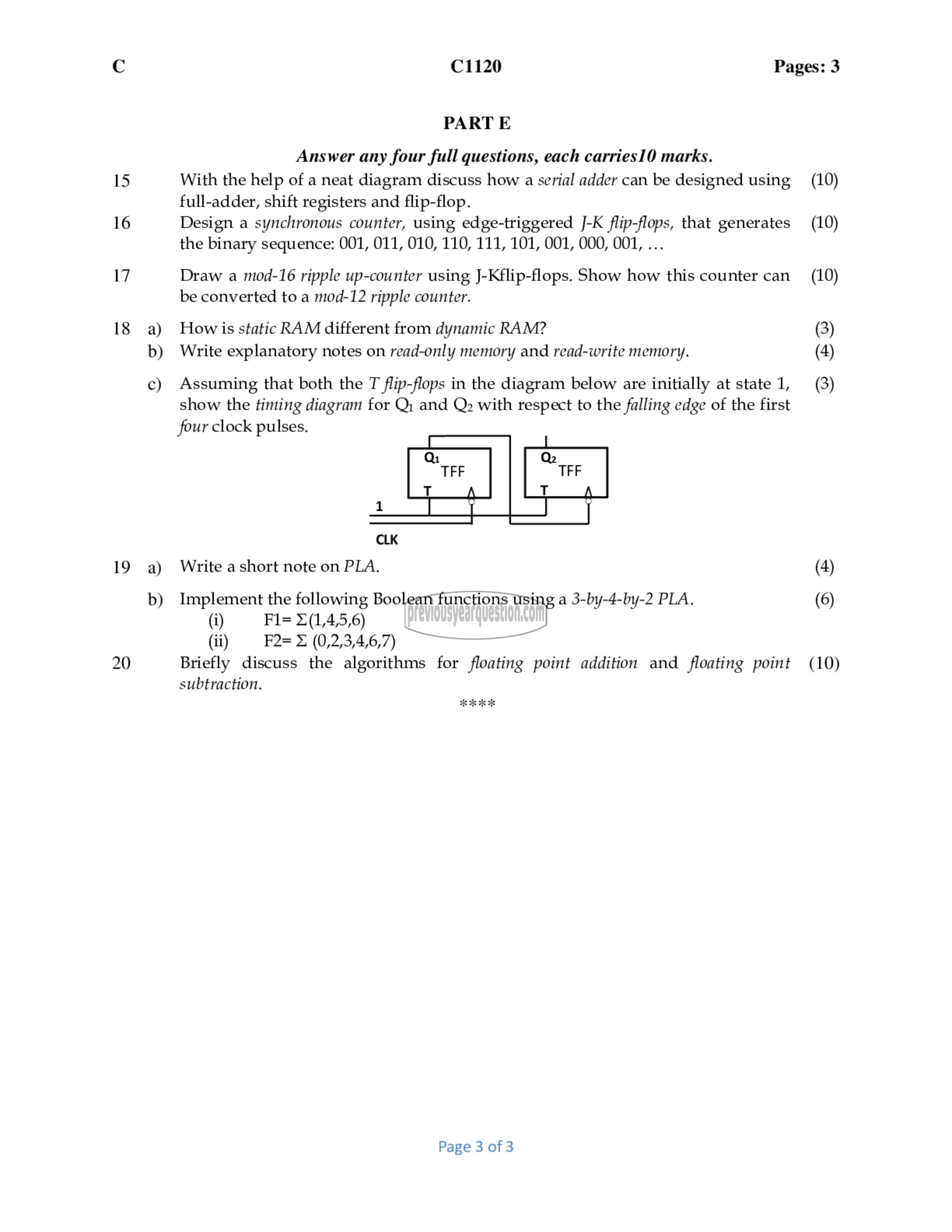

Assuming that both the T flip-flops in the diagram below are initially at state 1, (3)

show the timing diagram for ಟಿ; and 0 with respect to the falling edge of the first

four clock pulses.

CLK

Write a short note on PLA. (4)

Implement the following Boolean functions using a 3-by-4-by-2 PLA. (6)

(i) 115 X(1,4,5,6)

(ii) 72= ೫ (0,2,3,4,6,7)

Briefly discuss the algorithms for floating point addition and floating point (10)

subtraction.

¢ OK بد

Page 3 of 3