APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Switching Theory and Logic Design

Year : 2019

Term : MAY

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 203

Page:2

^ C1120 Pages: 3

PART C

Answer all questions, each carries3 marks.

8 Show how a master-slave J-K flip-flop can be realized using NOR and AND gates. (3)

9 Write the truth table of a 4x1 de-multiplexer and show the corresponding logic (3)

diagram.

10 Show how a full-subtractor can be implemented using a decoder. (3)

11 Realize a half-adder using NAND gates. (3)

PART D

Answer any two full questions, each carries 9 marks.

12 a) Implement the following Boolean functions using a 2X1 multiplexer and (3)

additional gates as needed: F(x,y,z) = >. (1,2,4,5).

b) Design a code converter with the following mapping specifications: (6)

Input code 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111

13 a) Given a 2-bit subtractor (block diagram), design a circuit with additional gates (3)

to use it as a comparator.

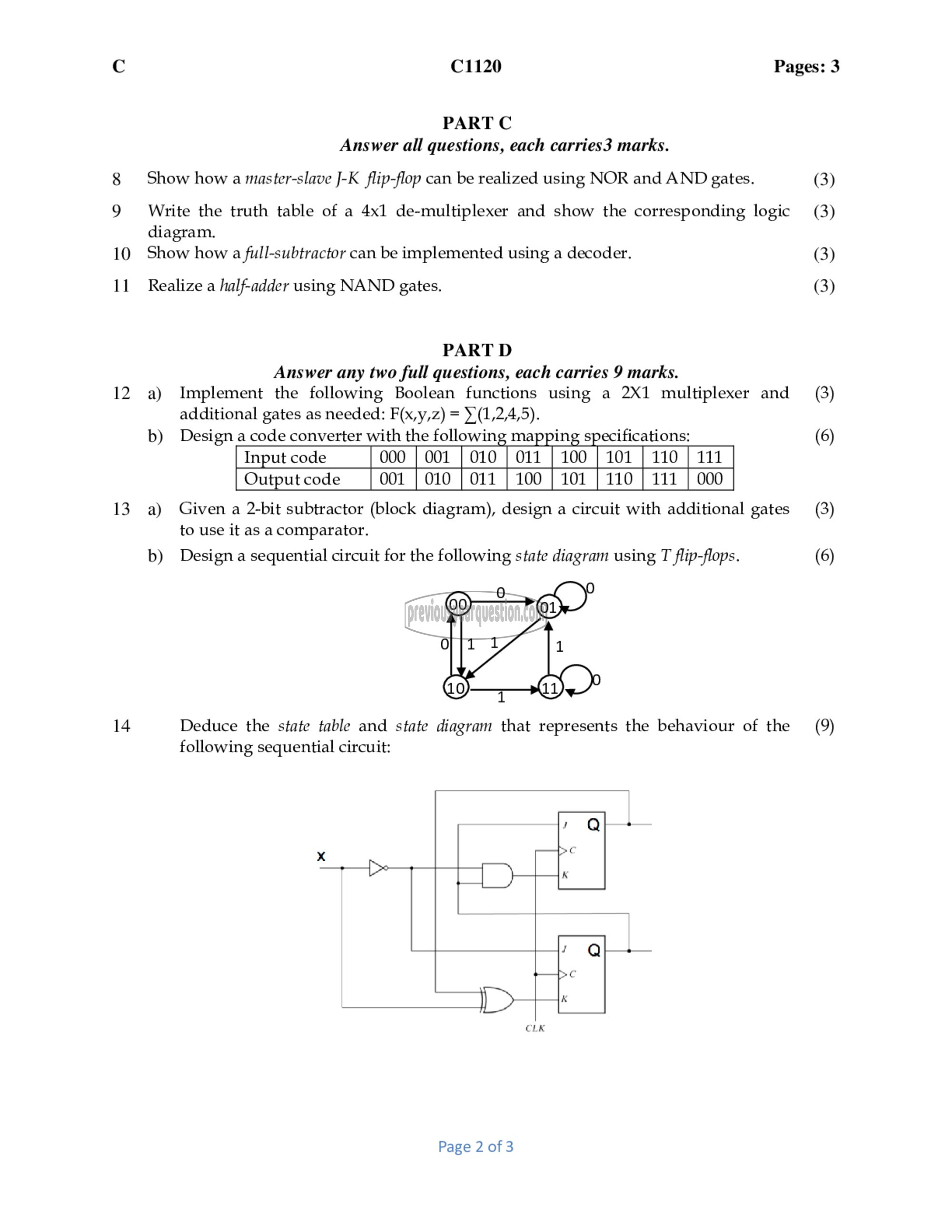

b) Design a sequential circuit for the following state diagram using T flip-flops. (6)

لی

0 | 1 1

1

14 Deduce the state table and state diagram that represents the behaviour of the (9)

following sequential circuit:

Page 2 of 3