APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Switching Theory and Logic Design

Year : 2018

Term : APRIL

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 203

Page:2

11

12

13

14

15

16

17

18

19

20

a)

b)

a)

b)

a)

b)

a)

b)

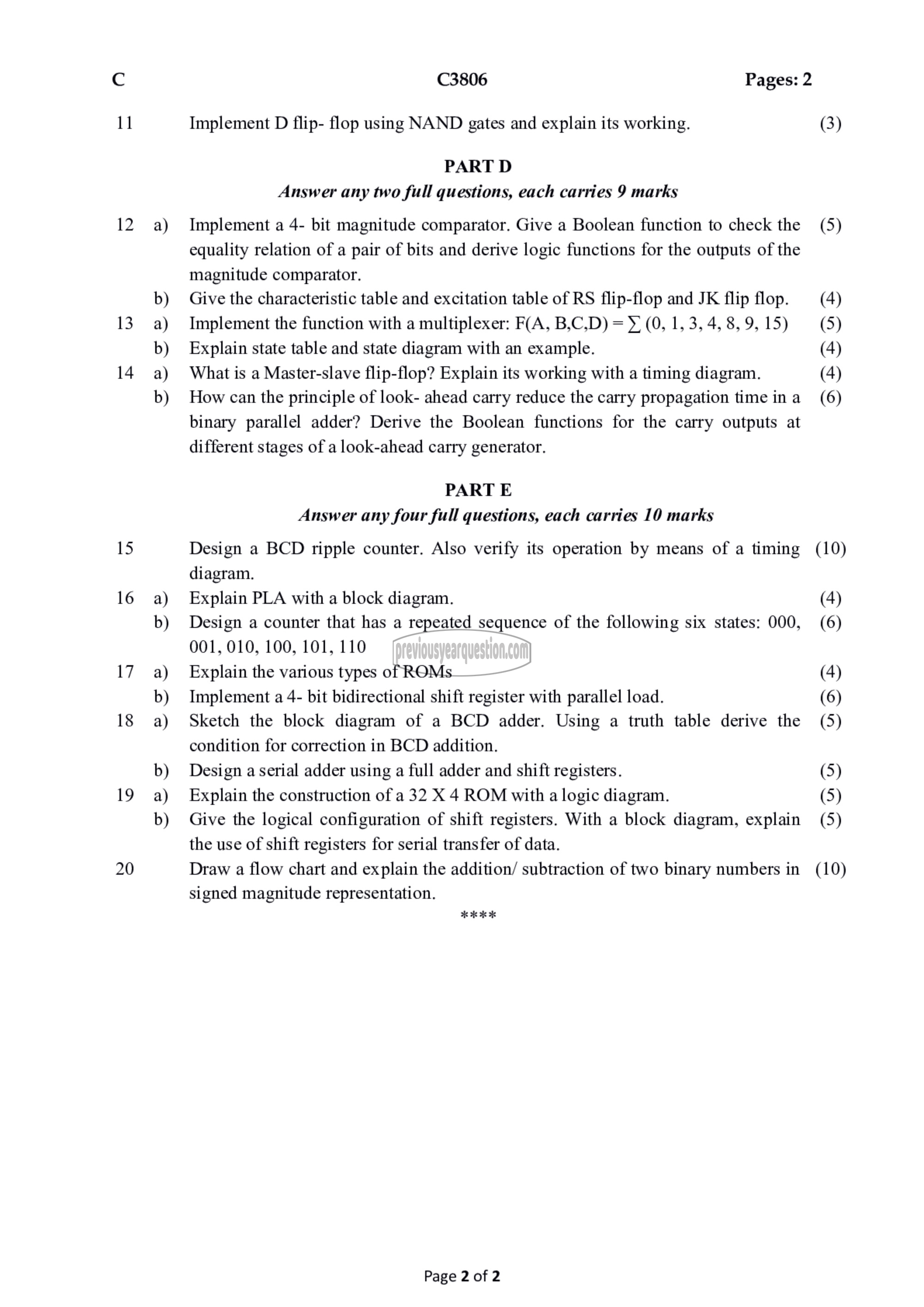

C3806 Pages: 2

Implement D flip- flop using NAND gates and explain its working.

PART D

Answer any two full questions, each carries 9 marks

Implement a 4- bit magnitude comparator. Give a Boolean function to check the

equality relation of a pair of bits and derive logic functions for the outputs of the

magnitude comparator.

Give the characteristic table and excitation table of RS flip-flop and JK flip flop.

Implement the function with a multiplexer: F(A, B,C,D) = ¥ (0, 1, 3, 4, 8, 9, 15)

Explain state table and state diagram with an example.

What is a Master-slave flip-flop? Explain its working with a timing diagram.

How can the principle of look- ahead carry reduce the carry propagation time in a

binary parallel adder? Derive the Boolean functions for the carry outputs at

different stages of a look-ahead carry generator.

PARTE

Answer any four full questions, each carries 10 marks

Design a BCD ripple counter. Also verify its operation by means of a timing

diagram.

Explain PLA with a block diagram.

Design a counter that has a repeated sequence of the following six states: 000,

001, 010, 100, 101, 110

Explain the various types of ROMs

Implement a 4- bit bidirectional shift register with parallel load.

Sketch the block diagram of a BCD adder. Using a truth table derive the

condition for correction in BCD addition.

Design a serial adder using a full adder and shift registers.

Explain the construction of a 32 % 4 ROM with a logic diagram.

Give the logical configuration of shift registers. With a block diagram, explain

the use of shift registers for serial transfer of data.

Draw a flow chart and explain the addition/ subtraction of two binary numbers in

signed magnitude representation.

11,

Page 2 of 2

(3)

(5)

(4)

(5)

(4)

(4)

(6)

(10)

(4)

(6)

(4)

(6)

(5)

(5)

(5)

(5)

(10)