APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 1

Subject : Digital Fundamentals

Year : 2017

Term : DECEMBER

Branch : MCA

Scheme : 2016 Full Time

Course Code : RLMCA 109

Page:1

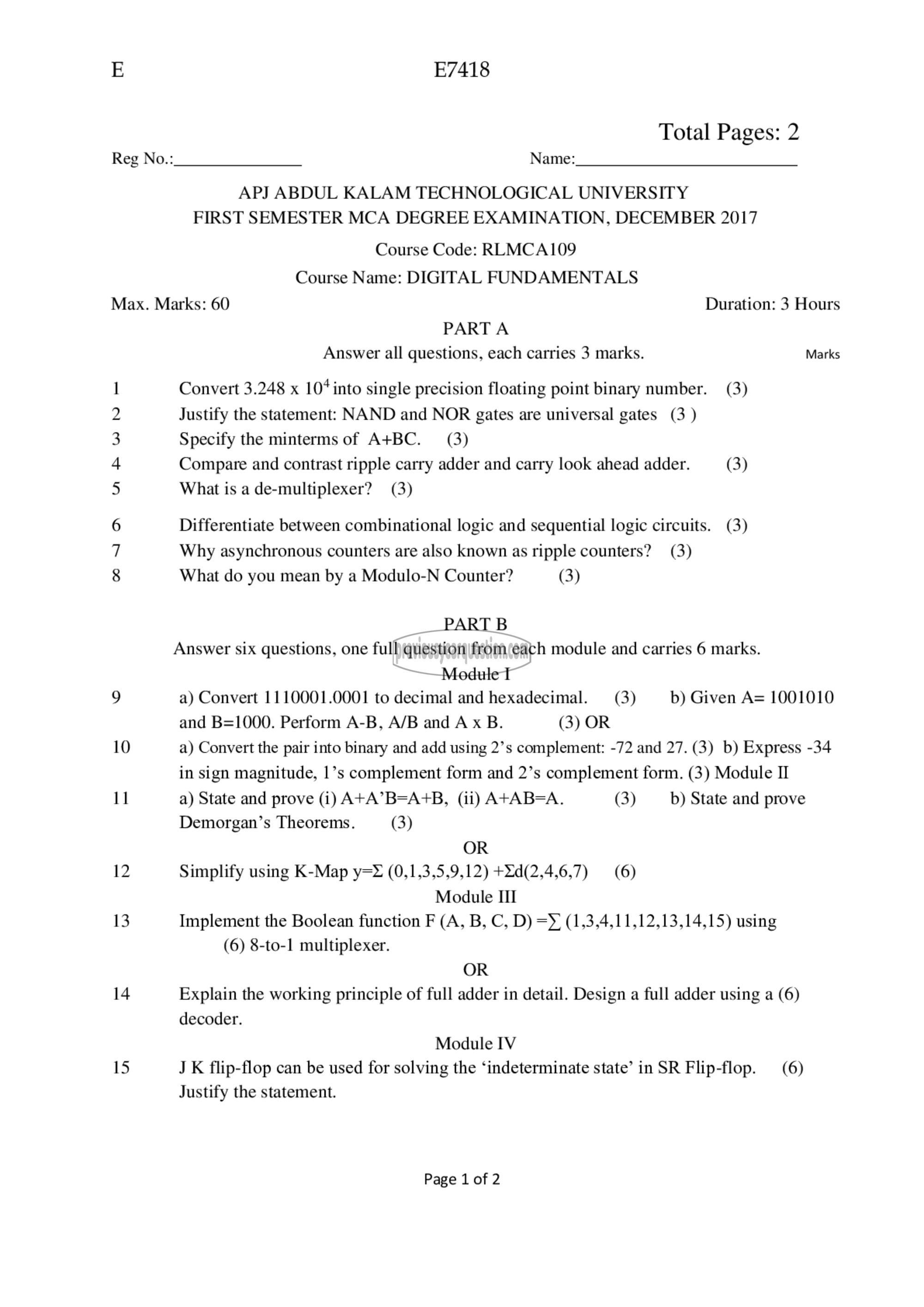

E E7418

Total Pages: 2

Reg No.: Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

FIRST SEMESTER MCA DEGREE EXAMINATION, DECEMBER 2017

Course Code: RLMCA109

Course Name: DIGITAL FUNDAMENTALS

Max. Marks: 60 Duration: 3 Hours

PART A

Answer all questions, each carries 3 marks. Marks

1 Convert 3.248 x 10" into single precision floating point binary number. (3)

2 Justify the statement: NAND and NOR gates are universal gates (3 )

3 Specify the minterms of A+BC. (3)

4 Compare and contrast ripple carry adder and carry look ahead adder. (3)

5 What is a de-multiplexer? (3)

6 Differentiate between combinational logic and sequential logic circuits. (3)

7 Why asynchronous counters are also known as ripple counters? (3)

8 What do you mean by a Modulo-N Counter? (3)

PART B

Answer six questions, one full question from each module and carries 6 marks.

Module I

9 a) Convert 1110001.0001 to decimal and hexadecimal. (3) b) Given A= 1001010

and B=1000. Perform A-B, A/B and A x B. (3) OR

10 a) Convert the pair into binary and add using 2’s complement: -72 and 27. (3) b) Express -34

in sign magnitude, 115 complement form and 2’s complement form. (3) Module II

11 a) State and prove (i) A+A’B=A+B, (ii) +^ 8 ಗಿ. (3) b) State and prove

Demorgan’s Theorems. (3)

OR

12 Simplify using K-Map y= (0,1,3,5,9,12) +2d(2,4,6,7) (6)

Module III

13 Implement the Boolean function F (A, 8, C, D) =>. (1,3,4,11,12,13,14,15) using

(6) 8-to-1 multiplexer.

OR

14 Explain the working principle of full adder in detail. Design a full adder using a (6)

decoder.

Module IV

15 J K flip-flop can be used for solving the ‘indeterminate state’ in SR Flip-flop. (6)

Justify the statement.

Page 1 of 2