APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Analog Electronic Circuits

Year : 2017

Term : JANUARY

Scheme : 2015 Full Time

Course Code : EE 203

Page:2

6 830045 Total Pages:4

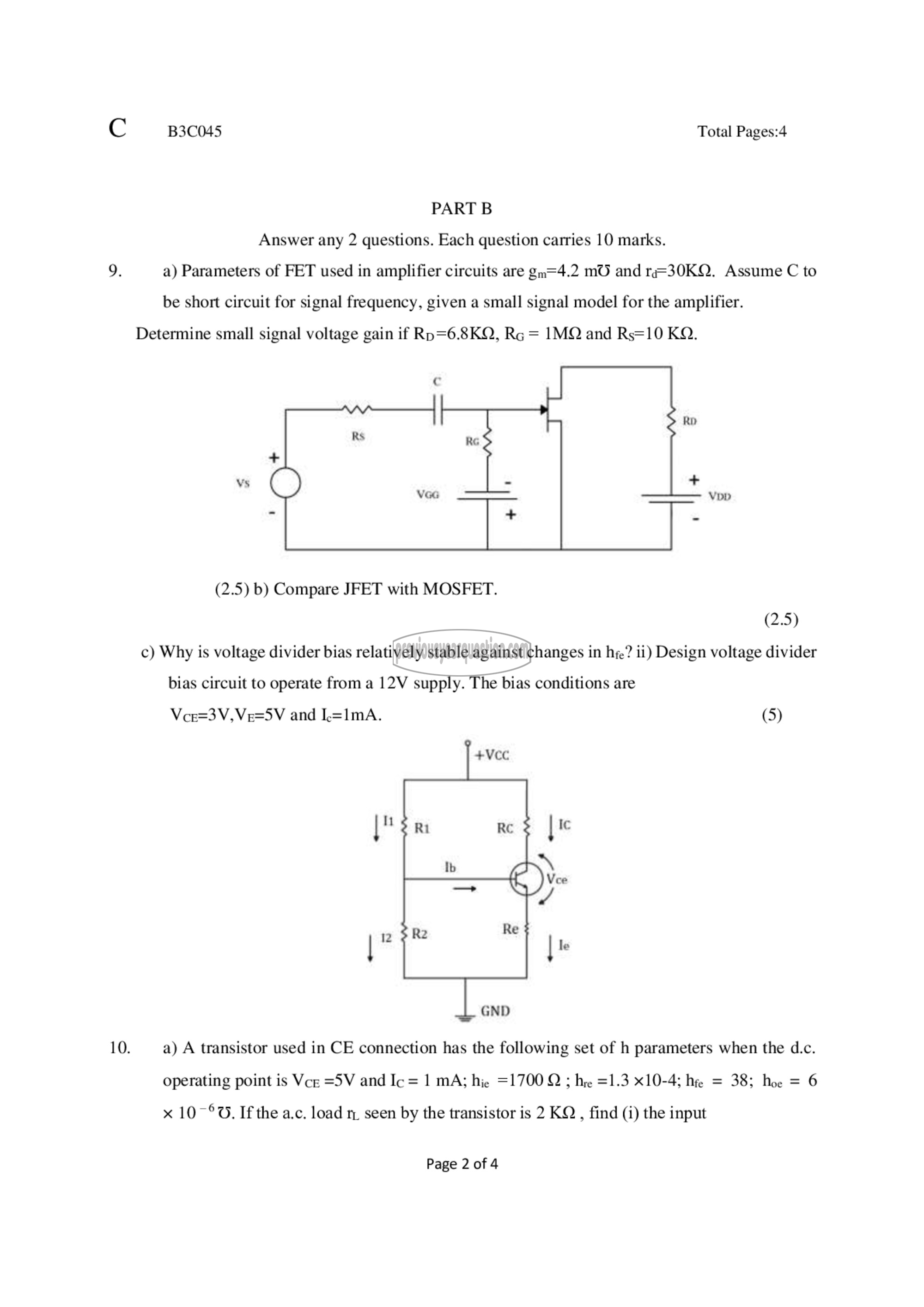

PART B

Answer any 2 questions. Each question carries 10 marks.

9. a) Parameters of FET used in amplifier circuits are gm=4.2 mU and ೧730142, Assume C to

be short circuit for signal frequency, given a small signal model for the amplifier.

Determine small signal voltage gain if Ro=6.8KQ, २५ = 10/6) and Rs=10 KQ.

vs

(2.5) b) Compare JFET with MOSFET.

(2.5)

௦) Why is voltage divider bias relatively stable against changes in டி? 11) Design voltage divider

bias circuit to operate from a 12V supply. The bias conditions are

Vce=3V,Ve=SV and [= 1111. (5)

10. a) A transistor used in CE connection has the following set of h parameters when the d.c.

operating point is ५४८5 =5V and Ic = 1 mA; hie 51700 Q ; hye =1.3 10-4; hee = 38; عمط = 6

x 10 ൦0. If the ೩.೦. load प, seen by the transistor 2 60) , find (i) the input

Page 2 of 4