APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Analog Electronic Circuits

Year : 2017

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EE 203

Page:1

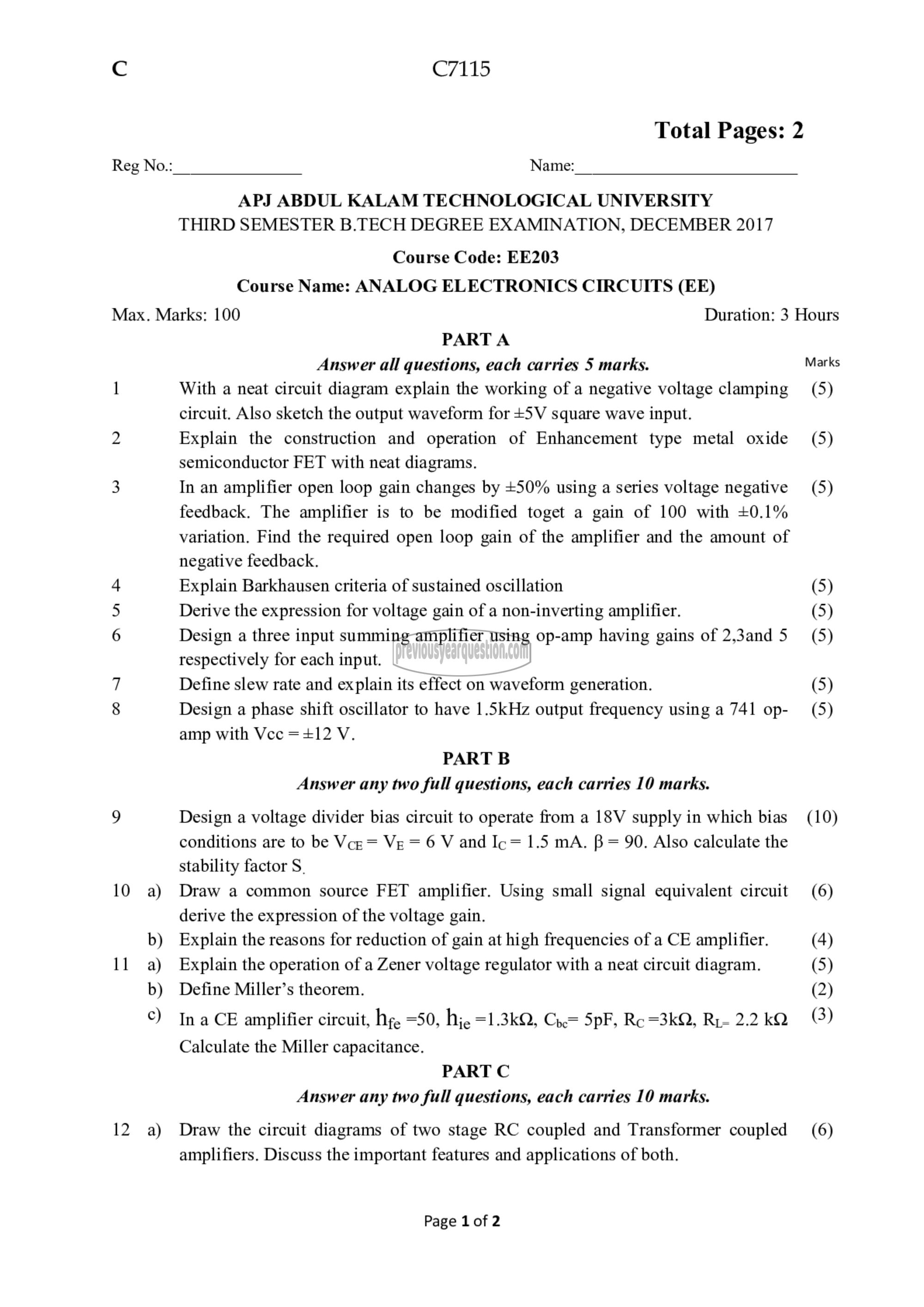

(0 C7115

Total Pages: 2

Reg No.: Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

THIRD SEMESTER B.TECH DEGREE EXAMINATION, DECEMBER 2017

Course Code: EE203

Course Name: ANALOG ELECTRONICS CIRCUITS (EE)

Max. Marks: 100 Duration: 3 Hours

PART A

Answer all questions, each carries 5 marks. Marks

1 With a neat circuit diagram explain the working of a negative voltage clamping (5)

circuit. Also sketch the output waveform for 2517 square wave input.

2 Explain the construction and operation of Enhancement type metal oxide (5)

semiconductor FET with neat diagrams.

3 In an amplifier open loop gain changes by +50% using a series voltage negative (5)

feedback. The amplifier is to be modified toget a gain of 100 with +0.1%

variation. Find the required open loop gain of the amplifier and the amount of

negative feedback.

4 Explain Barkhausen criteria of sustained oscillation (5)

5 Derive the expression for voltage gain of a non-inverting amplifier. (5)

6 Design a three input summing amplifier using op-amp having gains of 2,3and 5 (5)

respectively for each input.

7 Define slew rate and explain its effect on waveform generation. (5)

8 Design a phase shift oscillator to have 1.5kHz output frequency using a 741 op- (5)

amp with Vec = +12 V.

PART B

Answer any two full questions, each carries 10 marks.

9 Design a voltage divider bias circuit to operate from ೩ 18V supply in which bias (10)

conditions are to be Vcg= Vg = 6 V and 105 1.5 mA. B = 90. Also calculate the

stability factor 5.

10 a) Draw a common source FET amplifier. Using small signal equivalent circuit (6)

derive the expression of the voltage gain.

b) Explain the reasons for reduction of gain at high frequencies of a CE amplifier. (4)

11 ஐ Explain the operation of a Zener voltage regulator with a neat circuit diagram. (5)

b) Define Miller’s theorem. (2)

©) Ina CE amplifier circuit, hg. 550, വം =1.3kQ, ட 597, २८ =3kQ, ௩௨221 ಟೆ)

Calculate the Miller capacitance.

PART C

Answer any two full questions, each carries 10 marks.

12 2) Draw the circuit diagrams of two stage RC coupled and Transformer coupled (6)

amplifiers. Discuss the important features and applications of both.

Page 1 of 2