APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Logic Circuit Design

Year : 2017

Term : JANUARY

Scheme : 2015 Full Time

Course Code : EC 207

Page:2

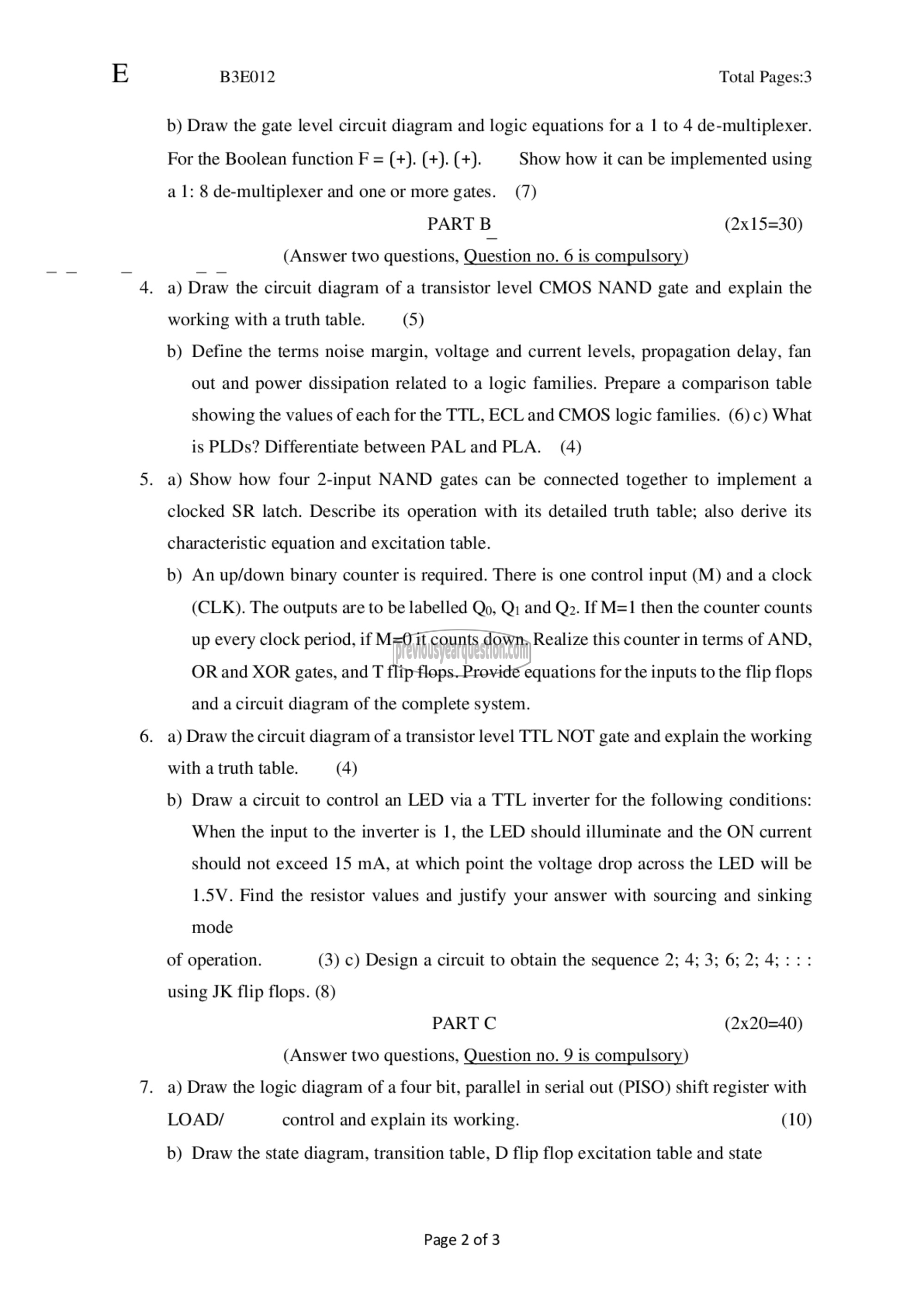

B3E012 Total Pages:3

b) Draw the gate level circuit diagram and logic equations for a 1 to 4 de-multiplexer.

For the Boolean function F = (+). (+). (+). Show how it can be implemented using

a 1: 8 de-multiplexer and one or more gates. (7)

PART B (2x15=30)

(Answer two questions, Question 10. 6 18 (۲مول وہہ no. 6 is compulsor

. ൭) Draw the circuit diagram of a transistor level CMOS NAND gate and explain the

working with a truth table. (5)

b) Define the terms noise margin, voltage and current levels, propagation delay, fan

out and power dissipation related to a logic families. Prepare a comparison table

showing the values of each for the TTL, ECL and CMOS logic families. (6) 0) What

is PLDs? Differentiate between PAL and PLA. (4)

. a) Show how four 2-input NAND gates can be connected together to implement a

clocked SR latch. Describe its operation with its detailed truth table; also derive its

characteristic equation and excitation table.

b) An up/down binary counter is required. There is one control input (M) and a clock

(CLK). The outputs are to be labelled Qo, Qi and 02. If M=1 then the counter counts

up every clock period, if M=0 it counts down. Realize this counter in terms of AND,

OR and XOR gates, and T flip flops. Provide equations for the inputs to the flip flops

and a circuit diagram of the complete system.

. a) Draw the circuit diagram of a transistor level TTL NOT gate and explain the working

with a truth table. (4)

b) Draw a circuit to control an LED via a TTL inverter for the following conditions:

When the input to the inverter is 1, the LED should illuminate and the ON current

should not exceed 15 mA, at which point the voltage drop across the LED will be

1.5V. Find the resistor values and justify your answer with sourcing and sinking

mode

of operation. (3) c) Design a circuit to obtain the sequence 2; 4; 3; 6; 2; 4: : : :

using JK flip flops. (8)

PART ^ (2x20=40)

(Answer two questions, Question no. 9 is compulsory)

. a) Draw the logic diagram of a four bit, parallel in serial out (PISO) shift register with

LOAD/ control and explain its working. (10)

b) Draw the state diagram, transition table, D flip flop excitation table and state

Page 2 of 3