APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 4

Subject : Digital Electronics and Logic Design

Year : 2019

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EE 204

Page:2

13

14

15

16

17

b)

a)

b)

a)

b)

a)

b)

a)

b)

a)

b)

D192038 Pages:2

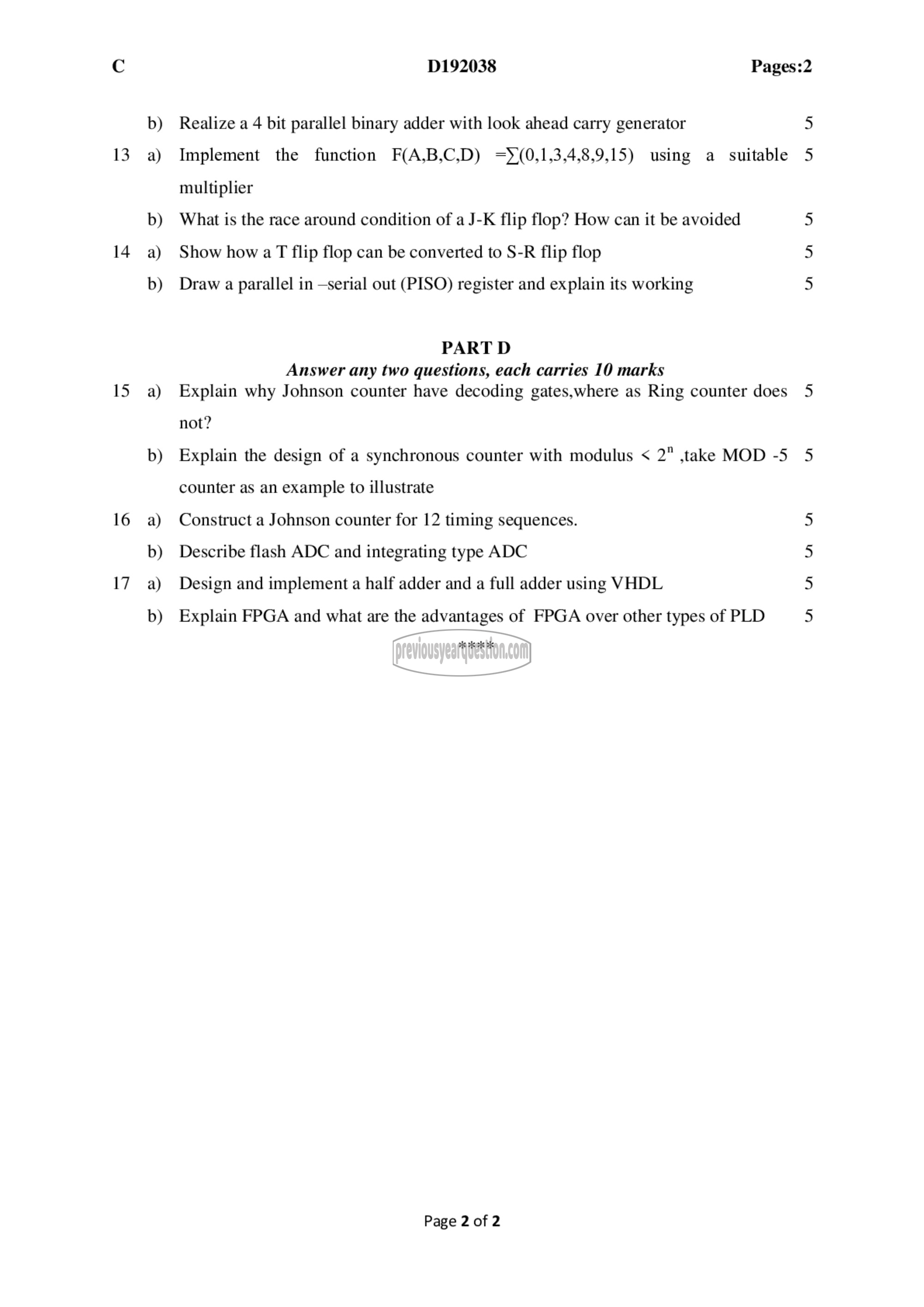

Realize a 4 bit parallel binary adder with look ahead carry generator

Implement the function F(A,B,C,D) ൭(0,1,3,4,8,9,15) using ೩ suitable

multiplier

What is the race around condition of a J-K flip flop? How can it be avoided

Show how a T flip flop can be converted to S-R flip flop

Draw a parallel in —serial out (PISO) register and explain its working

PART D

Answer any two questions, each carries 10 marks

Explain why Johnson counter have decoding gates,where as Ring counter does

not?

Explain the design of a synchronous counter with modulus ಇ 27 ,take MOD -5

counter as an example to illustrate

Construct a Johnson counter for 12 timing sequences.

Describe flash ADC and integrating type ADC

Design and implement a half adder and a full adder using VHDL

Explain FPGA and what are the advantages of FPGA over other types of PLD

Page 2 of 2

ما + ہا ما