APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 4

Subject : Digital Electronics and Logic Design

Year : 2019

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EE 204

Page:1

6

Reg No.:_ Name:

Max. Marks: 100

10

11

12

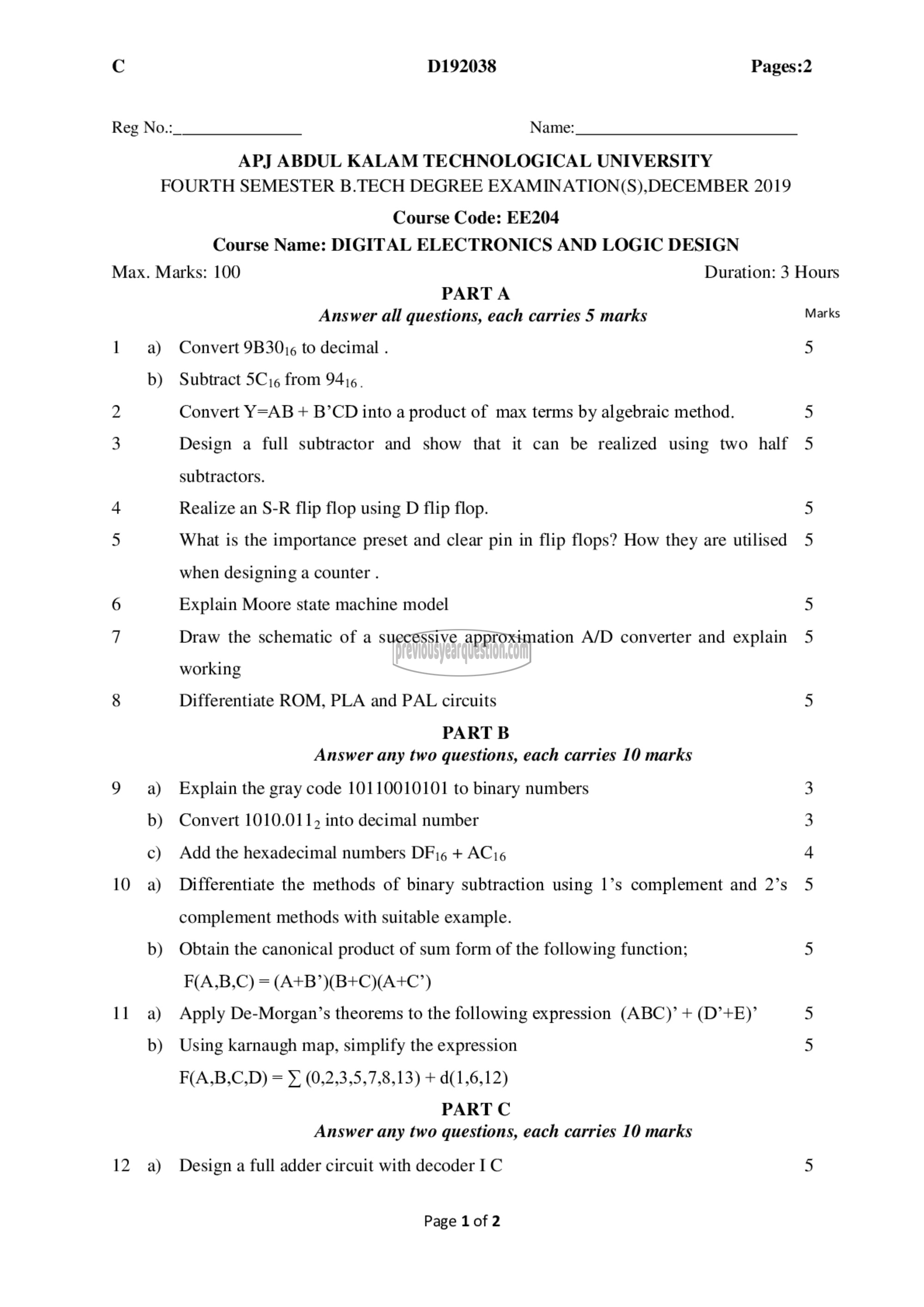

FOURTH SEMESTER B.TECH DEGREE EXAMINATION(S), DECEMBER 2019

a)

b)

a)

D192038 Pages:2

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

Course Code: EE204

Course Name: DIGITAL ELECTRONICS AND LOGIC DESIGN

PARTA

Answer all questions, each carries 5 marks

Convert 9830 to decimal .

Subtract 5Ci¢ from 9416.

Convert Y=AB + B’CD into a product of max terms by algebraic method.

Design a full subtractor and show that it can be realized using two half

subtractors.

Realize an S-R flip flop using D flip flop.

What is the importance preset and clear pin in flip flops? How they are utilised

when designing a counter .

Explain Moore state machine model

Draw the schematic of a successive approximation A/D converter and explain

working

Differentiate ROM, PLA and PAL circuits

PART تا

Answer any two questions, each carries 10 marks

Explain the gray code 10110010101 to binary numbers

Convert 1010.0112 into decimal number

Add the hexadecimal numbers 10716 + ACi6

Differentiate the methods of binary subtraction using 115 complement and 2’s

complement methods with suitable example.

Obtain the canonical product of sum form of the following function;

F(A,B,C) = (A+B’)(B+C)(A+C’)

Apply De-Morgan’s theorems to the following expression (ABC)’ + (D’+E)’

Using karnaugh map, simplify the expression

F(A,B,C,D) = >. (0,2,3,5,7,8,13) + d(1,6,12)

PART C

Answer any two questions, each carries 10 marks

Design a full adder circuit with decoder 1 C

Page 1 of 2

Duration: 3 Hours

Marks

5

ما

ما