APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

University : APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

Course : B.Tech

Semester : SEMESTER 4

Subject : Digital Electronics and Logic Design

Year : 2018

Term : APRIL

Scheme : 2015 Full Time

Course Code : EE 204

Page:2

PDF Text (Beta):

14

15

16

17

a)

b)

4809

Design a 4 bit Carry look ahead adder.

Answer any two questions, each carries 10 marks

PART D

Pages: 2

(10)

Design a counter to a given count sequence using T Flip flops 1, 2, 4, 6, 0, 5, (10)

Design a Flash type 2-bit ADC. What is the difficulty in designing ADCs of (10)

higher order bits?

Implement a half adder using VHDL.

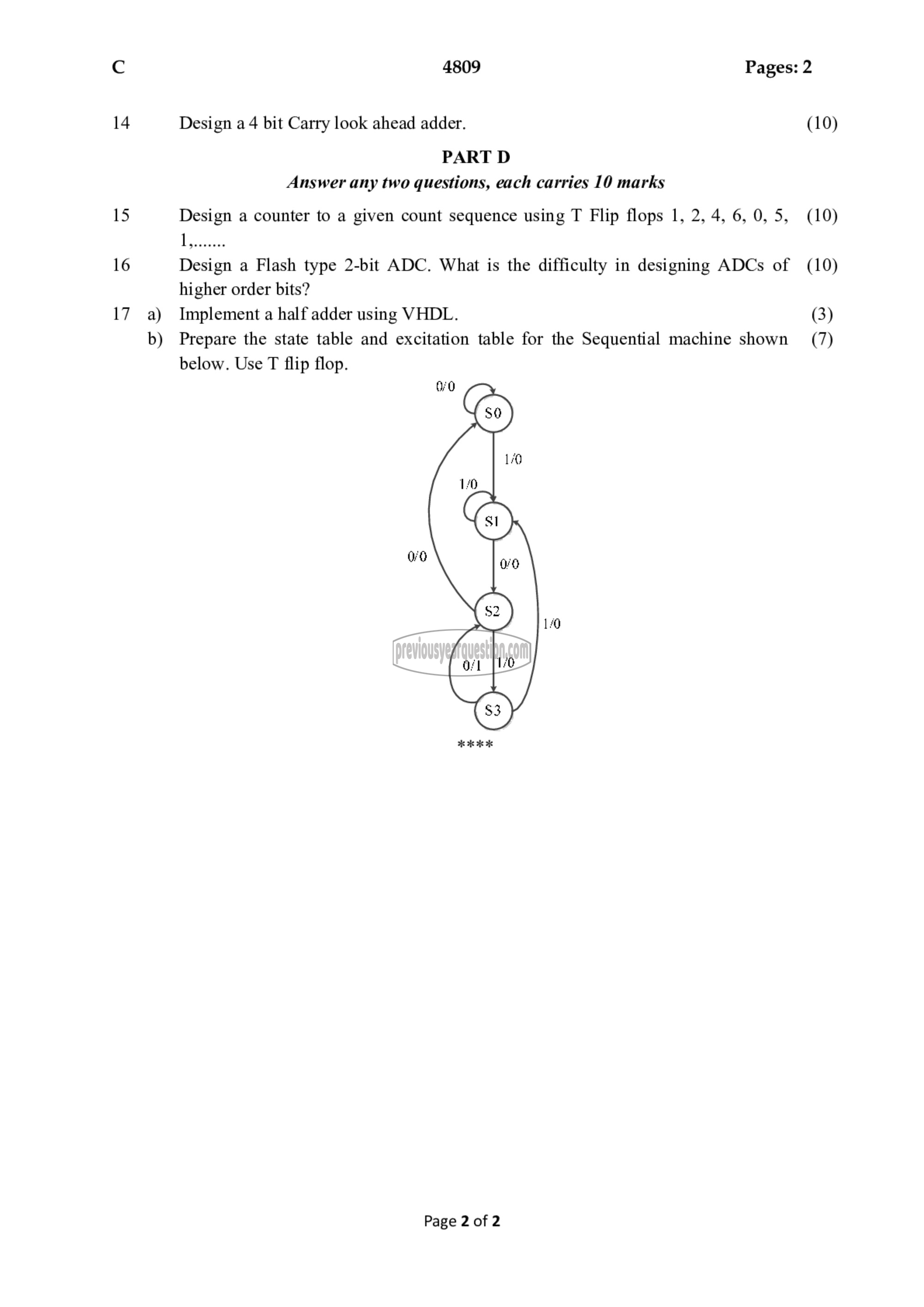

Prepare the state table and excitation table for the Sequential machine shown (7)

below. Use T flip flop.

1/0

0/0

اد ೫ ೫ بد

Page 2 of 2

(3)

Similar Question Papers

University of Calicut =>

M.A =>

SEMESTER 1 =>

Pre-Modern Kerala: Problems and Perspectives =>

2019 => MAY =>

Download

University of Calicut =>

B.Sc =>

SEMESTER 2 =>

Microbial Physiology and Taxonomy =>

2019 => MAY =>

Download

University of Calicut =>

B.Sc =>

SEMESTER 1 =>

Basic Logic and Number Theory =>

2022 => November =>

Download

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY =>

B.Tech =>

SEMESTER 4 =>

Computer Organization and Architecture =>

2018 => DECEMBER =>

Download

University of Calicut =>

B.Sc =>

SEMESTER 5 =>

Introduction to Geometry and Theory of Equations =>

2021 => NOVEMBER =>

Download