APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 4

Subject : Computer Organization and Architecture

Year : 2018

Term : APRIL

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 202

Page:1

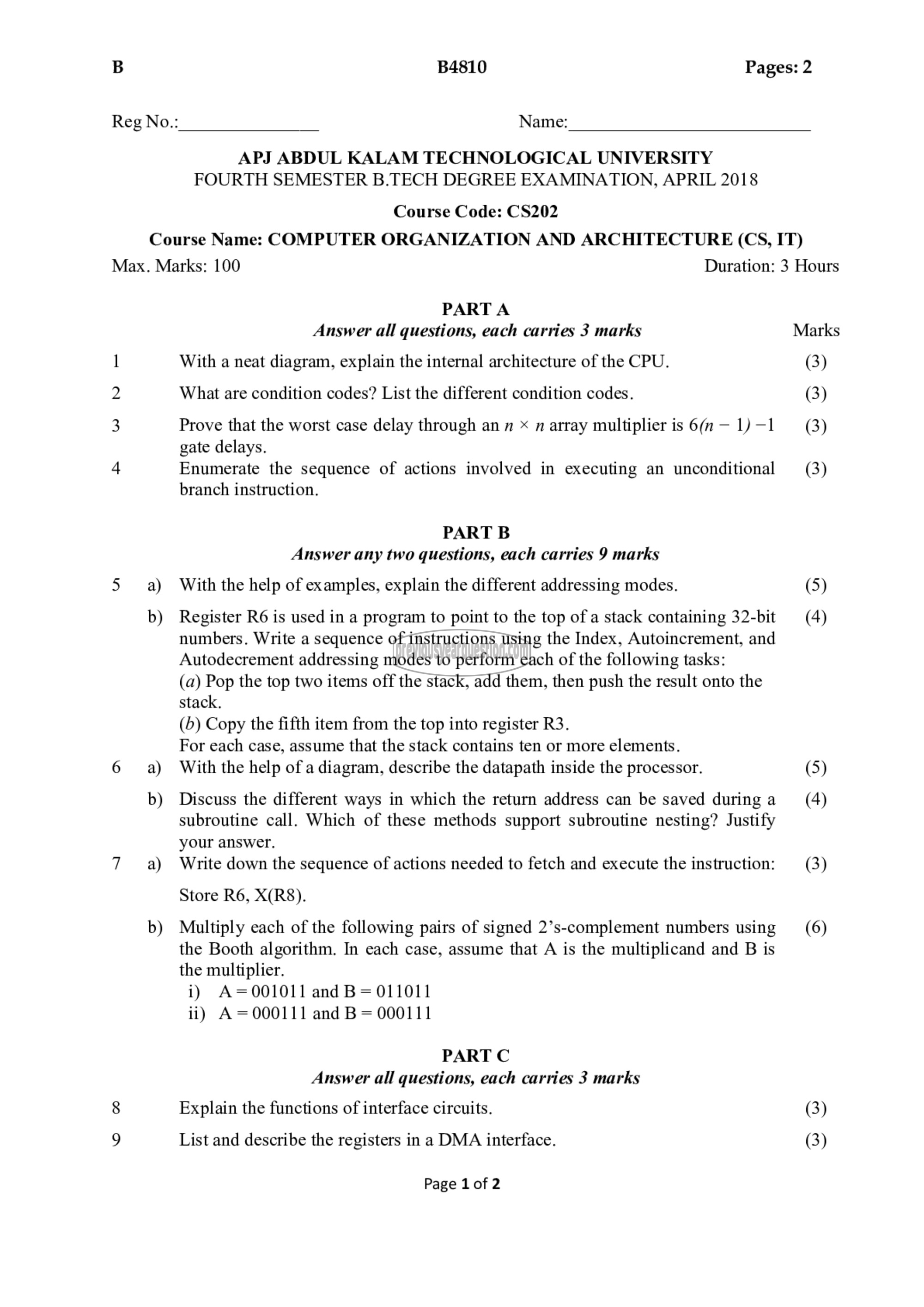

B B4810 Pages: 2

Reg No.: Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

FOURTH SEMESTER B.TECH DEGREE EXAMINATION, APRIL 2018

Course Code: CS202

Course Name: COMPUTER ORGANIZATION AND ARCHITECTURE (CS, IT)

Max. Marks: 100 Duration: 3 Hours

PART A

Answer all questions, each carries 3 marks Marks

1 With a neat diagram, explain the internal architecture of the CPU. (3)

2 What are condition codes? List the different condition codes. (3)

3 Prove that the worst case delay through ann × n array multiplier is 6(n—-—1)-1 (3)

gate delays.

4 Enumerate the sequence of actions involved in executing an unconditional (3)

branch instruction.

PART B

Answer any two questions, each carries 9 marks

5 ஐ With the help of examples, explain the different addressing modes. (5)

b) Register R6 is used in a program to point to the top of a stack containing 32-bit (4)

numbers. Write a sequence of instructions using the Index, Autoincrement, and

Autodecrement addressing modes to perform each of the following tasks:

(a) Pop the top two items off the stack, add them, then push the result onto the

stack.

(b) Copy the fifth item from the top into register R3.

For each case, assume that the stack contains ten or more elements.

6 a) With the help of 8 diagram, describe the datapath inside the processor. (5)

b) Discuss the different ways in which the return address can be saved duringa (4)

subroutine call. Which of these methods support subroutine nesting? Justify

your answer.

7 9) Write down the sequence of actions needed to fetch and execute the instruction: (3)

Store R6, X(R8).

b) Multiply each of the following pairs of signed 2’s-complement numbers using (6)

the Booth algorithm. In each case, assume that A is the multiplicand and B is

the multiplier.

1) A=001011 and 8 = 011011

ii) A=000111 and B= 000111

PART C

Answer all questions, each carries 3 marks

8 Explain the functions of interface circuits. (3)

9 List and describe the registers in a DMA interface. (3)

Page 1௦12