APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Logic Circuit Design

Year : 2019

Term : MAY

Scheme : 2015 Full Time

Course Code : EC 207

Page:2

a)

b)

a)

b)

a)

b)

a)

b)

C1150

Pages 2

Draw the circuit of a TTL NAND gate with totem pole output. Mention the (7)

advantages and disadvantages of totem pole configuration

Realize a J K flip-flop using D flip-flops

PART ^

Answer any two full questions, each carries20 marks.

(8)

Draw a serial input parallel output (4 bit) shift register. Convert this toa ring (10)

counter using suitable modifications

Draw the block diagram of a finite state machine. Differentiate between (10)

and Moore machine with the help of block diagrams

Design a 2 bit synchronous up/down counter using D flip-flop

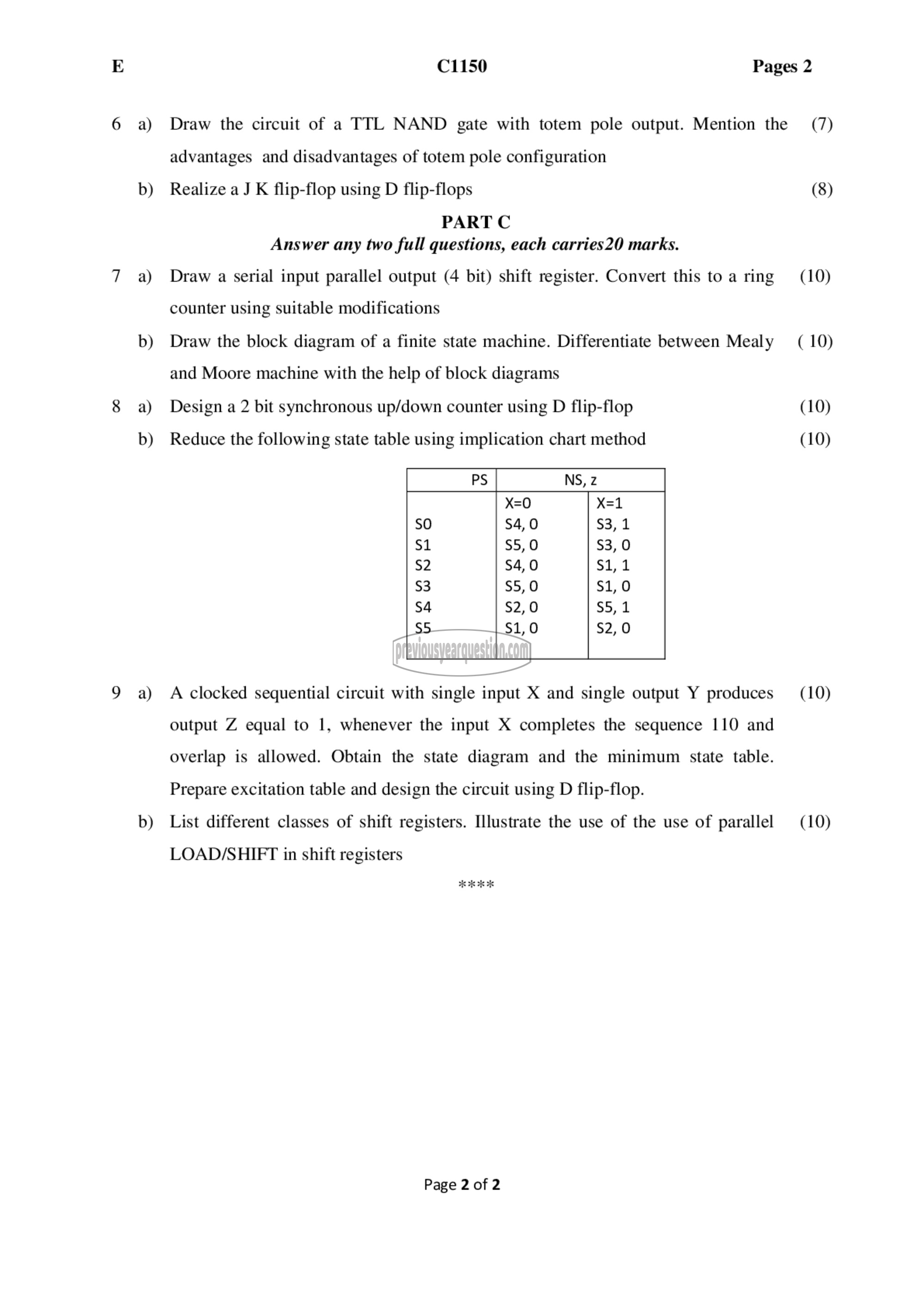

Reduce the following state table using implication chart method

50

51

52

53

54

55

PS

X=0

54,0

55,0

54,0

55, 0

52,0

51,0

(10)

(10)

A clocked sequential circuit with single input X and single output Y produces (10)

output Z equal to 1, whenever the input X completes the sequence 110 and

overlap is allowed. Obtain the state diagram and the minimum state table.

Prepare excitation table and design the circuit using D flip-flop.

List different classes of shift registers. Illustrate the use of the use of parallel (10)

LOAD/SHIFT in shift registers

Page 2 of 2