APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Logic Circuit Design

Year : 2018

Term : APRIL

Scheme : 2015 Full Time

Course Code : EC 207

Page:2

E E3836 Pages: 2

PART C

Answer any two full questions, each carries 20 marks

7 a) With the logic diagram explain the working of a four bit bi-directional Serial in (10)

Serial out (SISO) shift register with mode control.

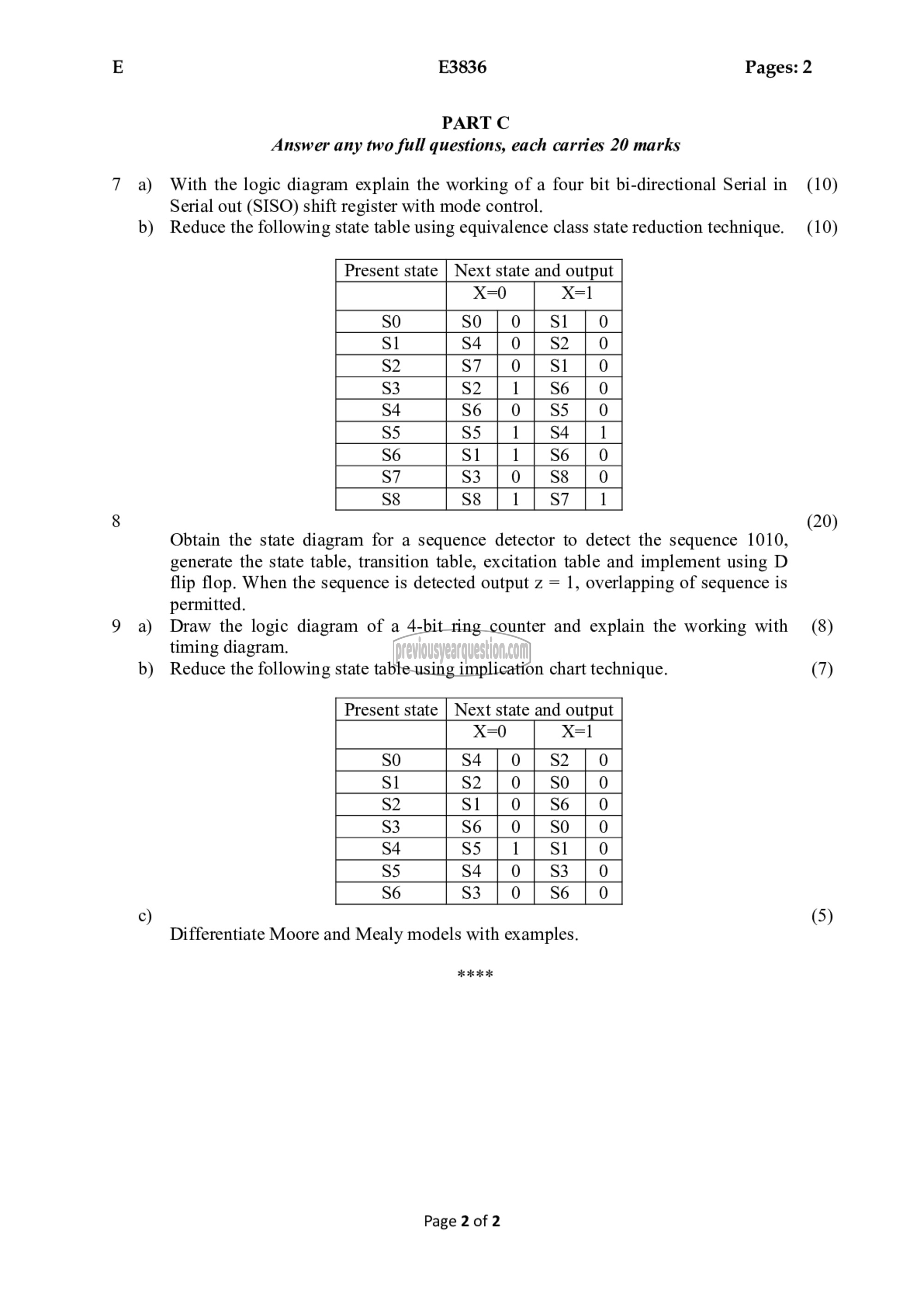

b) Reduce the following state table using equivalence class state reduction technique. (10)

Present state | Next state and output

8 20

Obtain the state diagram for a sequence detector to detect the sequence 1010, பர

generate the state table, transition table, excitation table and implement using D

flip flop. When the sequence is detected output z = 1, overlapping of sequence is

permitted.

9 a) Draw the logic diagram of a 4-bit ring counter and explain the working with (8)

timing diagram.

b) Reduce the following state table using implication chart technique. (7)

Present state | Next state and output

| 4 | 0 | @ | ८ | ८ | 2

Dl ७० |~ | > | >) | <> | نح

९) (5)

Differentiate Moore and Mealy models with examples.

मं ೫ ೫ ೫

Page 2 of 2