APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Logic Circuit Design

Year : 2017

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EC 207

Page:1

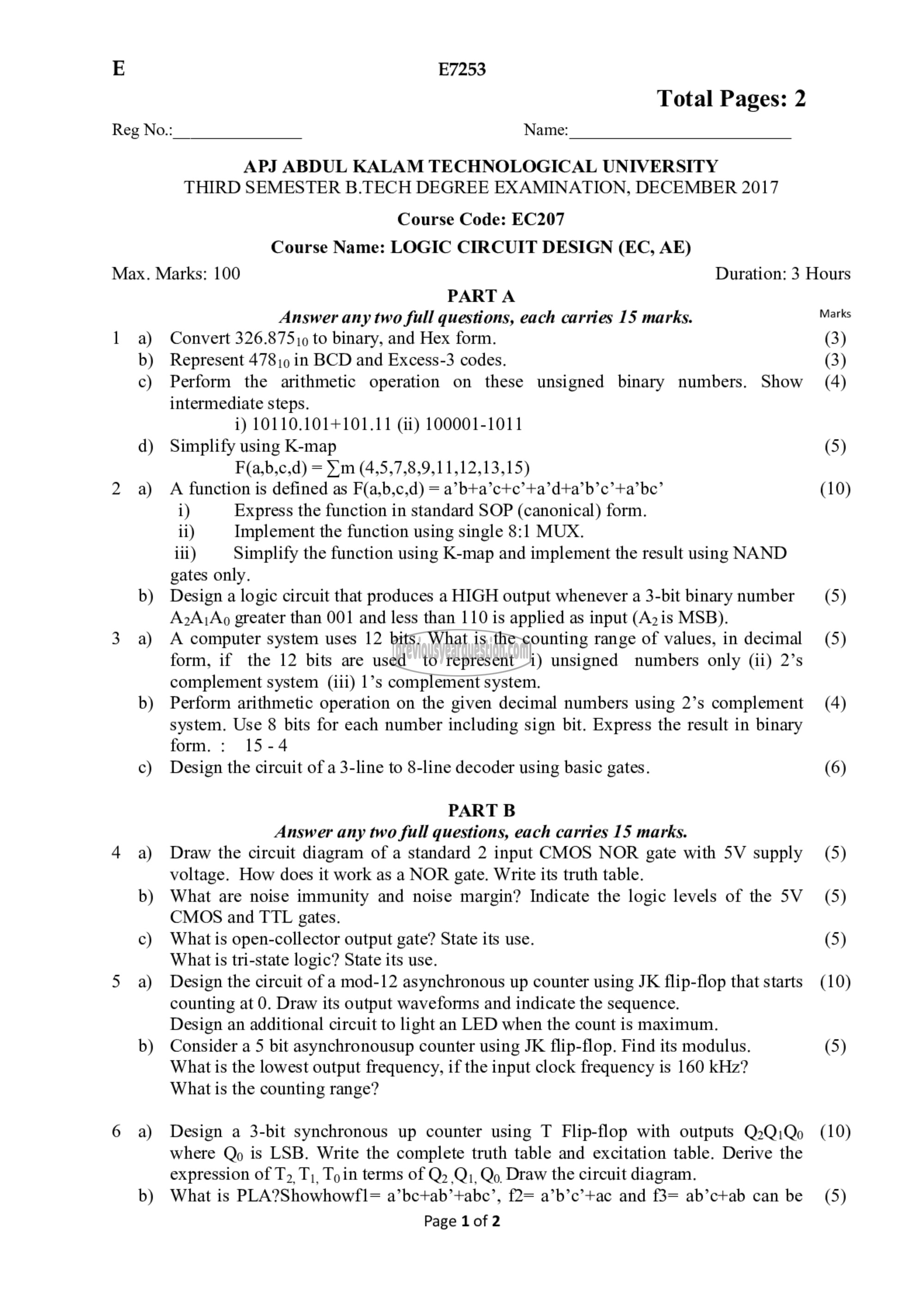

E E7253

Total Pages: 2

Reg No.: Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

THIRD SEMESTER B.TECH DEGREE EXAMINATION, DECEMBER 2017

Course Code: EC207

Course Name: LOGIC CIRCUIT DESIGN (EC, AE)

Max. Marks: 100 Duration: 3 Hours

PART A

Answer any two full questions, each carries 15 marks. Marks

1 a) Convert 326.875, to binary, and Hex form. (3)

b) Represent 47810 in BCD and Excess-3 codes. (3)

c) Perform the arithmetic operation on these unsigned binary numbers. Show (4)

intermediate steps.

i) 10110.101+101.11 (ii) 100001-1011

d) Simplify using K-map (5)

F(a,b,c,d) = 371 (4,5,7,8,9,11,12,13,15)

2 a) A function is defined as F(a,b,c,d) = a’bt+a’ctc’+a’d+a’b’c’+a’be’ (10)

i) Express the function in standard SOP (canonical) form.

ii) Implement the function using single 8:1 MUX.

111) Simplify the function using K-map and implement the result using NAND

gates only.

b) Design a logic circuit that produces a HIGH output whenever a 3-bit binary number (5)

^ 24140 greater than 001 and less than 110 is applied as input (A2is MSB).

3 2) A computer system uses 12 bits. What is the counting range of values, in decimal (5)

form, if the 12 bits are used to represent i) unsigned numbers only (ii) 2’s

complement system (iii) 15 complement system.

b) Perform arithmetic operation on the given decimal numbers using 2’s complement (4)

system. Use 8 bits for each number including sign bit. Express the result in binary

form. : 15-4

c) Design the circuit of a 3-line to 8-line decoder using basic gates. (6)

PART B

Answer any two full questions, each carries 15 marks.

4 a) Draw the circuit diagram of a standard 2 input CMOS NOR gate with ۷ذ supply (5)

voltage. How does it work as a NOR gate. Write its truth table.

b) What are noise immunity and noise margin? Indicate the logic levels of the 57 (5)

CMOS and TTL gates.

c) What is open-collector output gate? State its use. (5)

What is tri-state logic? State its use.

5 a) Design the circuit of a mod-12 asynchronous up counter using JK flip-flop that starts (10)

counting at 0. Draw its output waveforms and indicate the sequence.

Design an additional circuit to light an LED when the count is maximum.

b) Consider ೩ 5 bit asynchronousup counter using JK flip-flop. Find its modulus. (5)

What is the lowest output frequency, if the input clock frequency is 160 kHz?

What is the counting range?

6 a) Design a 3-bit synchronous up counter using T Flip-flop with outputs 9൮൭൦ (10)

where Qo is LSB. Write the complete truth table and excitation table. Derive the

expression of T, 11 Toin terms of ൮ 01 Qo, Draw the circuit diagram.

b) What is PLA?Showhowfl= a’bct+ab’+abc’, f2= a’b’c’+ac and f3= ab’ctab can be (5)

Page 1 of 2