APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 4

Subject : Computer Organization

Year : 2017

Term : JULY

Scheme : 2015 Full Time

Course Code : EC 206

Page:2

a)

b)

a)

b)

a)

b)

a)

b)

B4D0382

OR

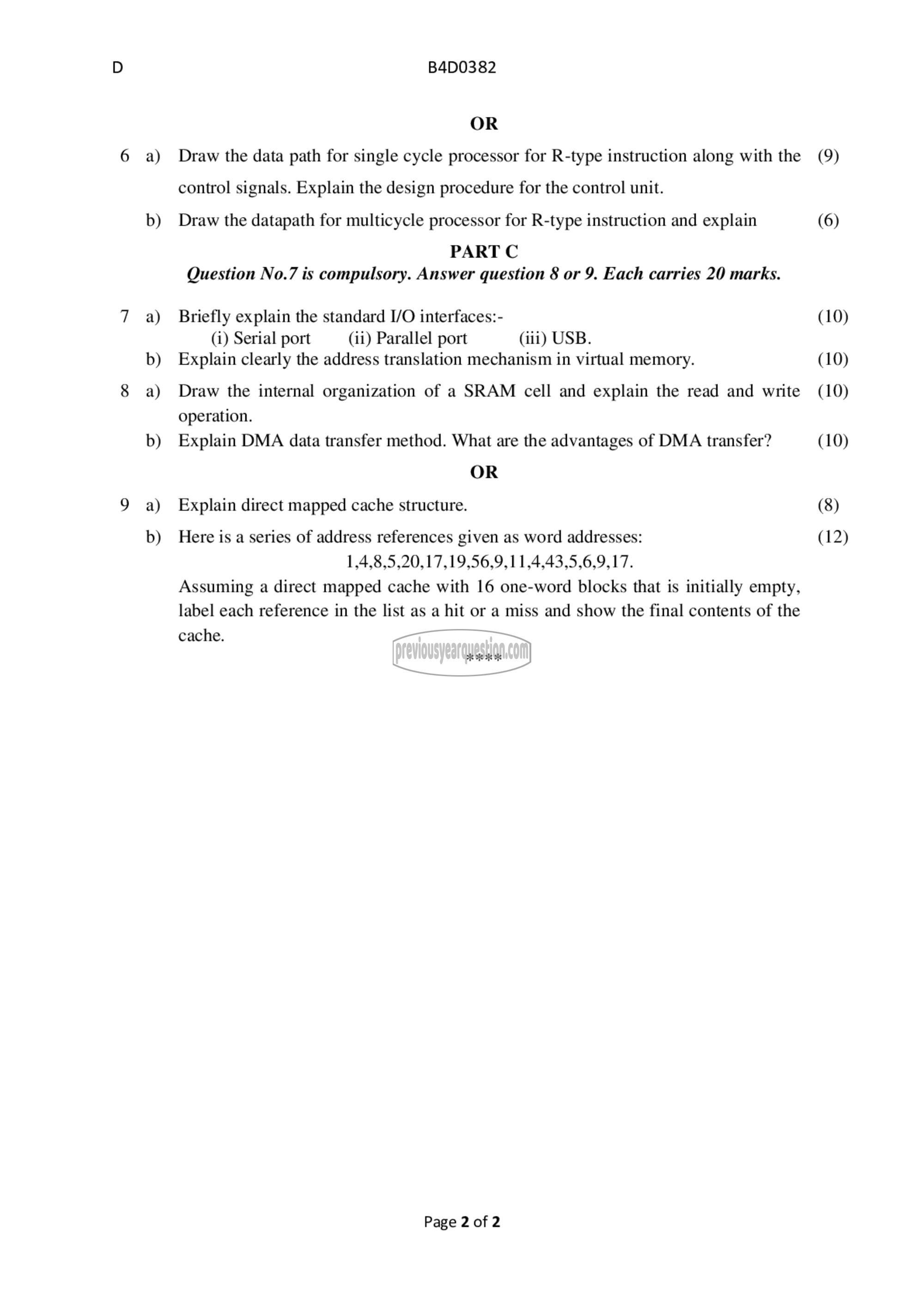

Draw the data path for single cycle processor for R-type instruction along with the

control signals. Explain the design procedure for the control unit.

Draw the datapath for multicycle processor for R-type instruction and explain

PART C

Question No.7 is compulsory. Answer question 8 or 9. Each carries 20 marks.

Briefly explain the standard I/O interfaces:-

(i) Serial port (ii) Parallel port (11) USB.

Explain clearly the address translation mechanism in virtual memory.

Draw the internal organization of a SRAM cell and explain the read and write

operation.

Explain DMA data transfer method. What are the advantages of DMA transfer?

OR

Explain direct mapped cache structure.

Here is a series of address references given as word addresses:

1,4,8,5,20,17,19,56,9,11,4,43,5,6,9,17.

Assuming a direct mapped cache with 16 one-word blocks that is initially empty,

label each reference in the list as a hit or a miss and show the final contents of the

cache.

بد بد oR

Page 2 of 2

(9)

(6)

(10)

(10)

(10)

(10)

(8)

(12)