APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 4

Subject : Computer Organization

Year : 2017

Term : JULY

Scheme : 2015 Full Time

Course Code : EC 206

Page:1

Reg No.: Name:

Max. Marks: 100

b)

b)

0)

0)

௦)

b)

0)

0)

8400382

Total Pages: 2

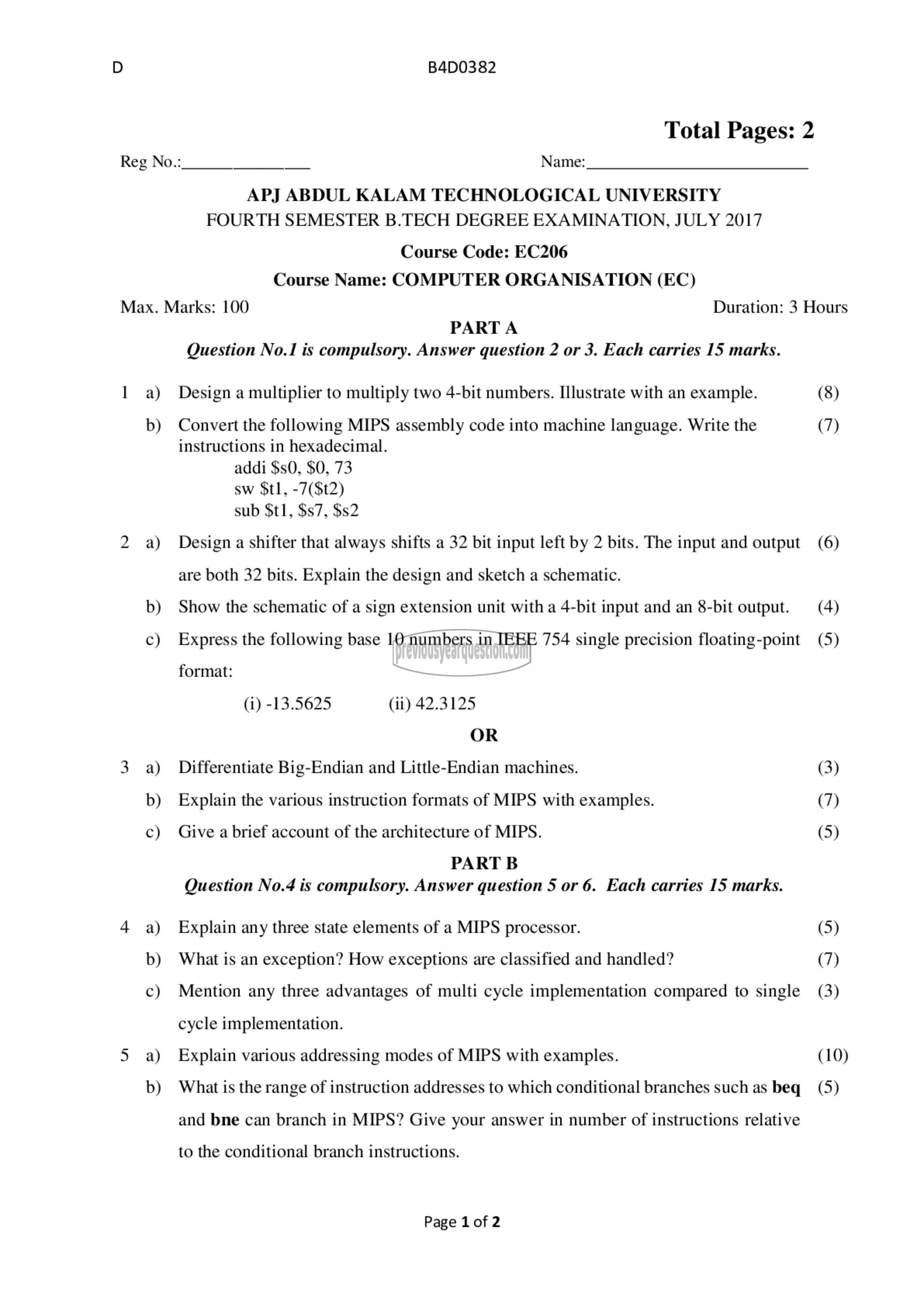

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

FOURTH SEMESTER B.TECH DEGREE EXAMINATION, JULY 2017

Course Code: EC206

Course Name: COMPUTER ORGANISATION (EC)

PARTA

Question No.1 is compulsory. Answer question 2 or 3. Each carries 15 marks.

Design a multiplier to multiply two 4-bit numbers. Illustrate with an example.

Convert the following MIPS assembly code into machine language. Write the

instructions in hexadecimal.

addi $s0, $0, 73

sw $tl, -7($t2)

sub 81, $s2

Design a shifter that always shifts a 32 bit input left by 2 bits. The input and output

are both 32 bits. Explain the design and sketch a schematic.

Show the schematic of a sign extension unit with a 4-bit input and an 8-bit output.

Express the following base 10 numbers in IEEE 754 single precision floating-point

format:

(1) -13.5625 (ii) 42.3125

OR

Differentiate Big-Endian and Little-Endian machines.

Explain the various instruction formats of MIPS with examples.

Give a brief account of the architecture of MIPS.

PART B

Question No.4 is compulsory. Answer question 5 or 6. Each carries 15 marks.

Explain any three state elements of a MIPS processor.

What is an exception? How exceptions are classified and handled?

Mention any three advantages of multi cycle implementation compared to single

cycle implementation.

Explain various addressing modes of MIPS with examples.

What is the range of instruction addresses to which conditional branches such as beq

and bne can branch in MIPS? Give your answer in number of instructions relative

to the conditional branch instructions.

Page 1 of 2

Duration: 3 Hours

(8)

(7)

(6)

(4)

(5)

(3)

(7)

(5)

(5)

(7)

(3)

(10)

(5)