APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 7

Subject : Digital Signal Processing

Year : 2020

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EE 407

Page:1

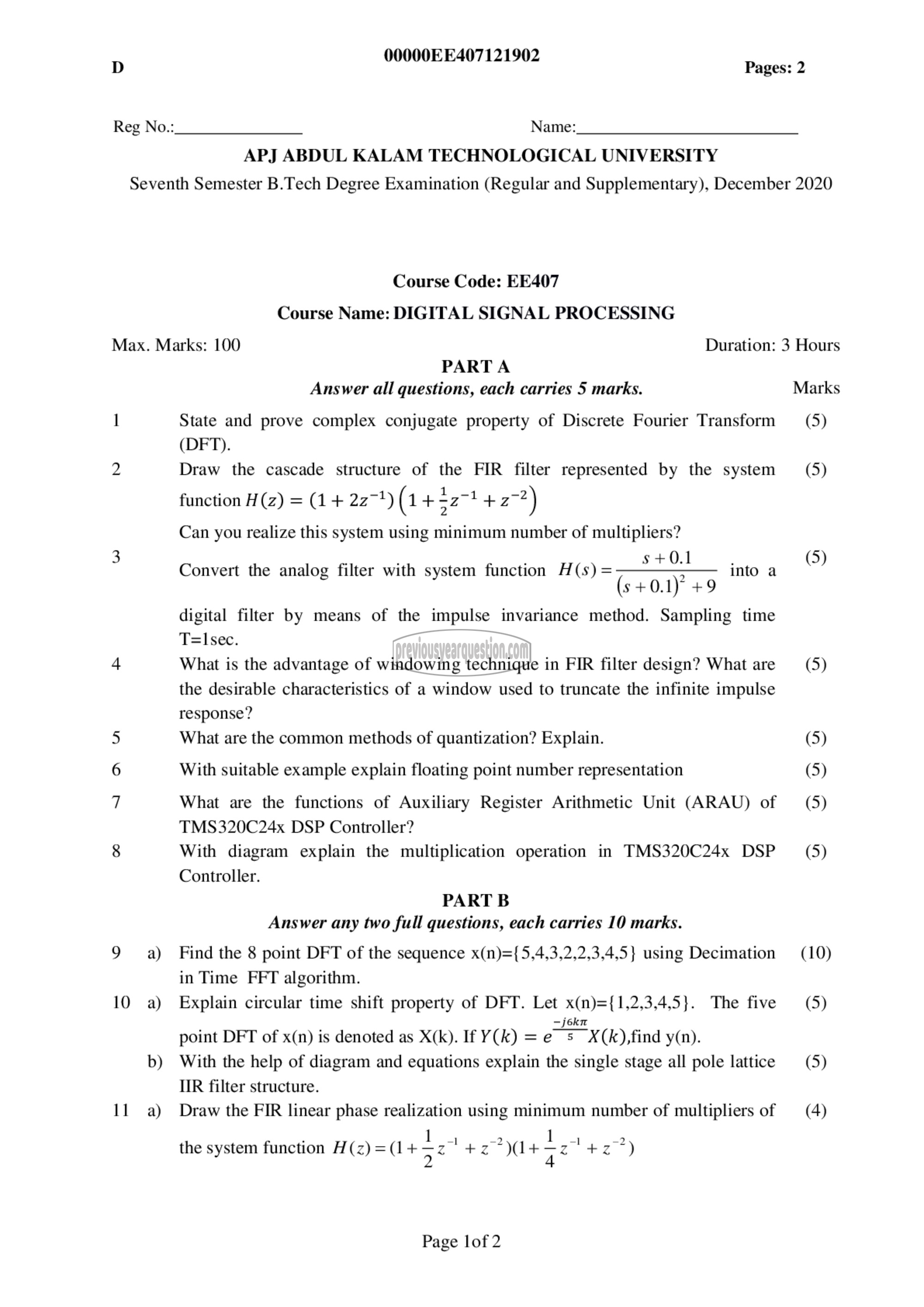

> 00000EE407121902 Pages: 2

Reg No.: Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

Seventh Semester B.Tech Degree Examination (Regular and Supplementary), December 2020

Course Code: EE407

Course Name: DIGITAL SIGNAL PROCESSING

Max. Marks: 100 Duration: 3 Hours

PARTA

Answer all questions, each carries 5 marks. Marks

1 State and prove complex conjugate property of Discrete Fourier Transform (5)

(DFT).

2 Draw the cascade structure of the FIR filter represented by the system (5)

function H(z) = (1 + 2271) (1 + بوڈ + 22]

Can you realize this system using minimum number of multipliers?

8 Convert the analog filter with system function H இடை تھا into a ©)

($ + 0.1) +9

digital filter by means of the impulse invariance method. Sampling time

1-156.

4 What is the advantage of windowing technique in FIR filter design? What are (5)

the desirable characteristics of a window used to truncate the infinite impulse

response?

5 What are the common methods of quantization? Explain. (5)

6 With suitable example explain floating point number representation (5)

7 What are the functions of Auxiliary Register Arithmetic Unit (ARAU) of (5)

TMS320C24x DSP Controller?

8 With diagram explain the multiplication operation ൧ TMS320C24x 9 (5)

Controller.

PART تا

Answer any two full questions, each carries 10 marks.

9 a) Find the 8 point DFT of the sequence x(n)={5,4,3,2,2,3,4,5} using Decimation (10)

in Time FFT algorithm.

10 a) Explain circular time shift property of DFT. Let x(n)={1,2,3,4,5}. The five (5)

—j6kn

point DFT of x(n) is denoted as X(k). If Y(k) = ௪ ~ X(k),find y(n).

b) With the help of diagram and equations explain the single stage all pole lattice (5)

IIR filter structure.

11 a) Draw the FIR linear phase realization using minimum number of multipliers of (4)

the system function H(z) = )1 + அ 45514 qe +z)

Page lof 2