APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Switching Theory and Logic Design

Year : 2017

Term : JANUARY

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 203

Page:1

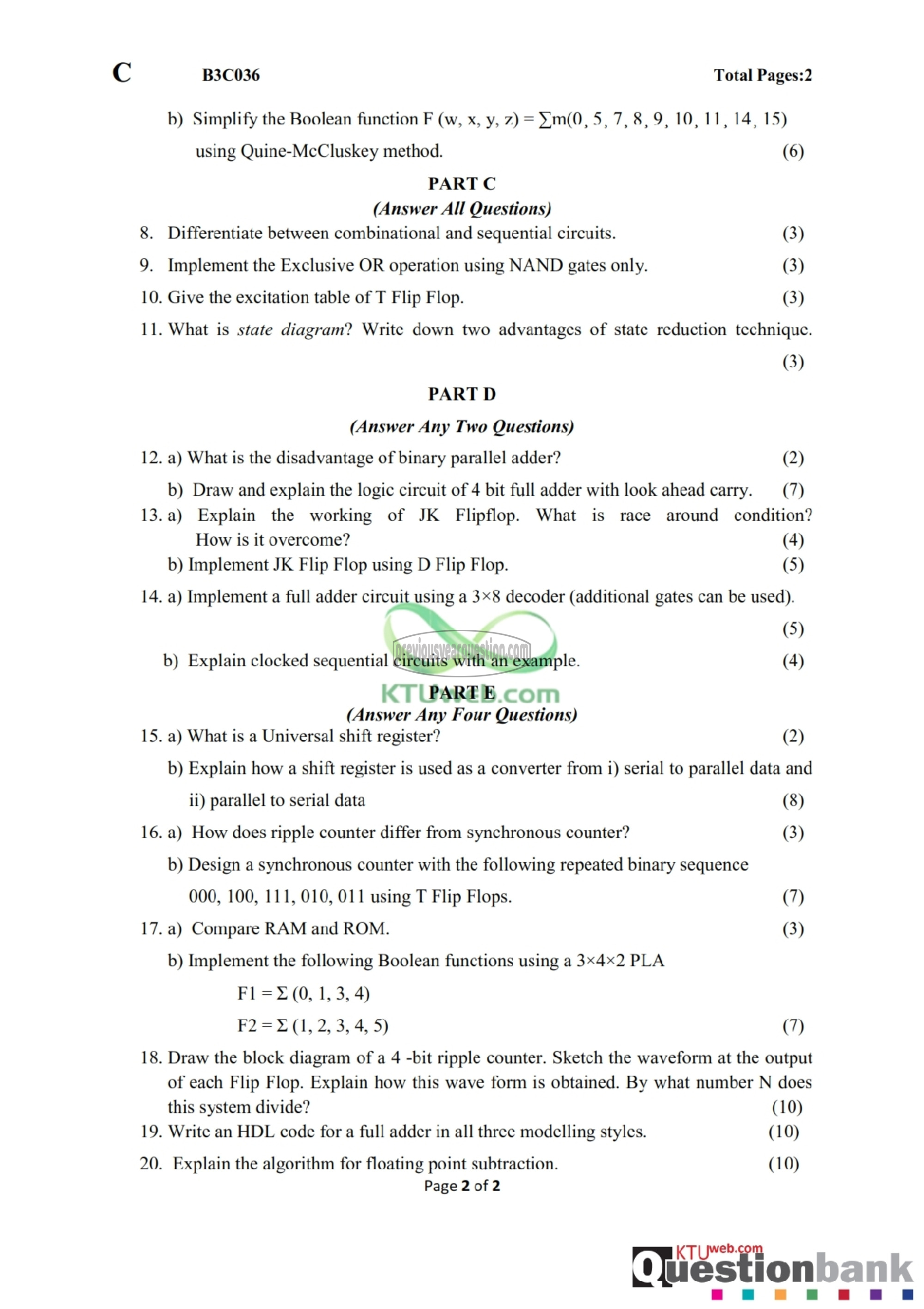

C B3C036 Total Pages:2

b) Simplify the Boolean function F (w, x, ೫, 7) = 3. 711(0, 5, 7, 8,9, 10,11, 14, 15)

using Quine-McCluskey method. (6)

PART C

(Answer All Questions)

8. Differentiate between combinational and sequential circuits. (3)

9. Implement the Exclusive OR operation using NAND gates only. (3)

10. Give the excitation table of T Flip Flop. (3)

11. What is state diagram? Write down two advantages of state reduction technique.

(3)

PART D

(Answer Any Two Questions)

12. a) What is the disadvantage of binary parallel adder? (2)

b) Draw and explain the logic circuit of 4 bit full adder with look ahead carry. (7)

13.a) Explain the working of JK Flipflop. What is race around condition?

How is it overcome? (4)

b) Implement JK Flip Flop using D Flip Flop. (5)

14. a) Implement a full adder iw) using a 3x8 decoder (additional gates can be used).

(5)

b) Explain clocked sequential سی le (4)

1 பிக com

(Answer Any Four Questions)

15. a) What is a Universal shift register? (2)

b) Explain how a shift register is used as a converter from 1) serial to parallel data and

ii) parallel to serial data (8)

16. a) How does ripple counter differ from synchronous counter? (3)

b) Design a synchronous counter with the following repeated binary sequence

000, 100, 111, 010, 011 using T Flip Flops. (7)

17. a) Compare RAM and ROM. (3)

b) Implement the following Boolean functions using ೩ 3x4x2 PLA

Fl = 2 (0, 1, 3, 4)

F2 = > (1, 2, 3, 4, 5) (7)

18. Draw the block diagram of a 4 -bit ripple counter. Sketch the waveform at the output

of each Flip Flop. Explain how this wave form is obtained. By what number N does

this system divide? (10)

19. Write an HDL code for a full adder in all three modelling styles. (10)

20. Explain the algorithm for floating point subtraction. (10)

Page 2 of 2

KT UP

uestionbank