APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 5

Subject : Digital System Design

Year : 2020

Term : SEPTEMBER

Scheme : 2015 Full Time

Course Code : EC 361

Page:2

a)

b)

९)

a)

b)

a)

b)

a)

b)

00000EC361121902

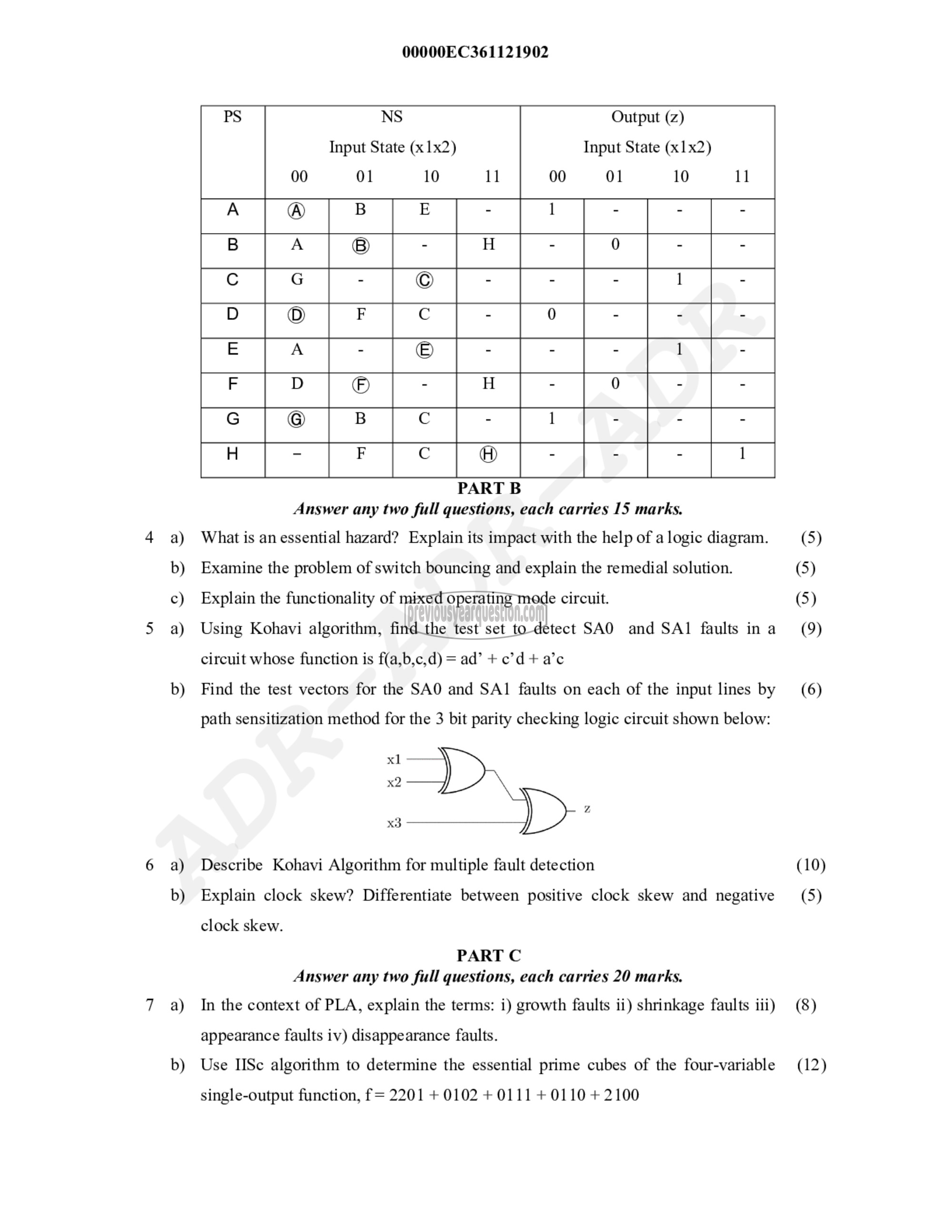

NS

Input State (x 1x2)

Output (z)

Input State (x1x2)

Answer any two full questions, each carries 15 marks.

What is an essential hazard? Explain its impact with the help of a logic diagram. (5)

Examine the problem of switch bouncing and explain the remedial solution. (5)

Explain the functionality of mixed operating mode circuit. (5)

Using Kohavi algorithm, find the test set to detect SAO and SAI faults ina (9)

circuit whose function is f(a,b,c,d) = ad’ + ५१५ + 8௦

Find the test vectors for the SAO and 881 faults on each of the input lines by (6)

path sensitization method for the 3 bit parity checking logic circuit shown below:

xl Ds

x2

2

x3

Describe Kohavi Algorithm for multiple fault detection (10)

Explain clock skew? Differentiate between positive clock skew and negative (5)

clock skew.

PART C

Answer any two full questions, each carries 20 marks.

In the context of PLA, explain the terms: i) growth faults ii) shrinkage faults iii) (8)

appearance faults iv) disappearance faults.

Use 115൦ algorithm to determine the essential prime cubes of the four-variable (12)

single-output function, f= 2201 + 0102 + 0111 + 0110 0