APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 1

Subject : Digital Fundamentals

Year : 2018

Term : JULY

Branch : MCA

Scheme : 2016 Full Time

Course Code : RLMCA 109

Page:1

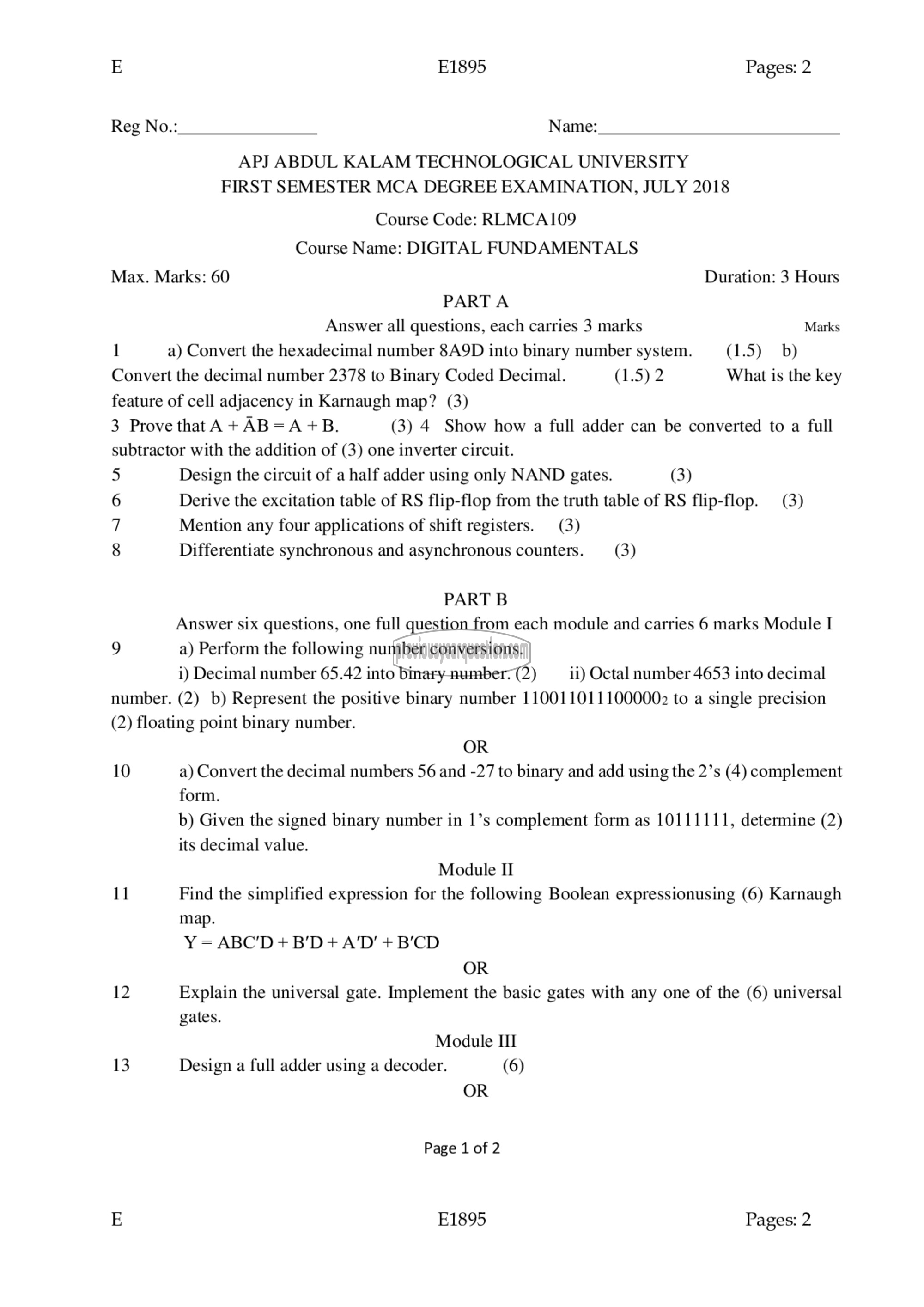

E E1895 Pages: 2

Reg No.: Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

FIRST SEMESTER MCA DEGREE EXAMINATION, JULY 2018

Course Code: 09

Course Name: DIGITAL FUNDAMENTALS

Max. Marks: 60 Duration: 3 Hours

PART A

Answer all questions, each carries 3 marks Marks

1 a) Convert the hexadecimal number 8A9D into binary number system. (1.5) 0)

Convert the decimal number 2378 to Binary Coded Decimal. (1.5) 2 What is the key

feature of cell adjacency in Karnaugh map? (3)

3 Prove that A +AB=A+B. (3) 4 Show how a full adder can be converted to a full

subtractor with the addition of (3) one inverter circuit.

5 Design the circuit of a half adder using only NAND gates. (3)

6 Derive the excitation table of RS flip-flop from the truth table of RS flip-flop. (3)

7 Mention any four applications of shift registers. (3)

8 Differentiate synchronous and asynchronous counters. (3)

PART 8

Answer six questions, one full question from each module and carries 6 marks Module I

9 a) Perform the following number conversions.

i) Decimal number 65.42 into binary number. (2) ii) Octal number 4653 into decimal

number. (2) b) Represent the positive binary number 1100110111000002 to a single precision

(2) floating point binary number.

OR

10 a) Convert the decimal numbers 56 and -27 to binary and add using the 2’s (4) complement

form.

b) Given the signed binary number in 1’s complement form as 10111111, determine (2)

its decimal value.

Module II

11 Find the simplified expression for the following Boolean expressionusing (6) Karnaugh

map.

Y = ൧3൬ + 817 + A'D' + B'CD

OR

12 Explain the universal gate. Implement the basic gates with any one of the (6) universal

gates.

Module III

13 Design a full adder using a decoder. (6)

OR

Page 1 of 2

E E1895 Pages: 2