APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 5

Subject : Digital System Design

Year : 2019

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EC 361

Page:2

F 01005 Pages:3

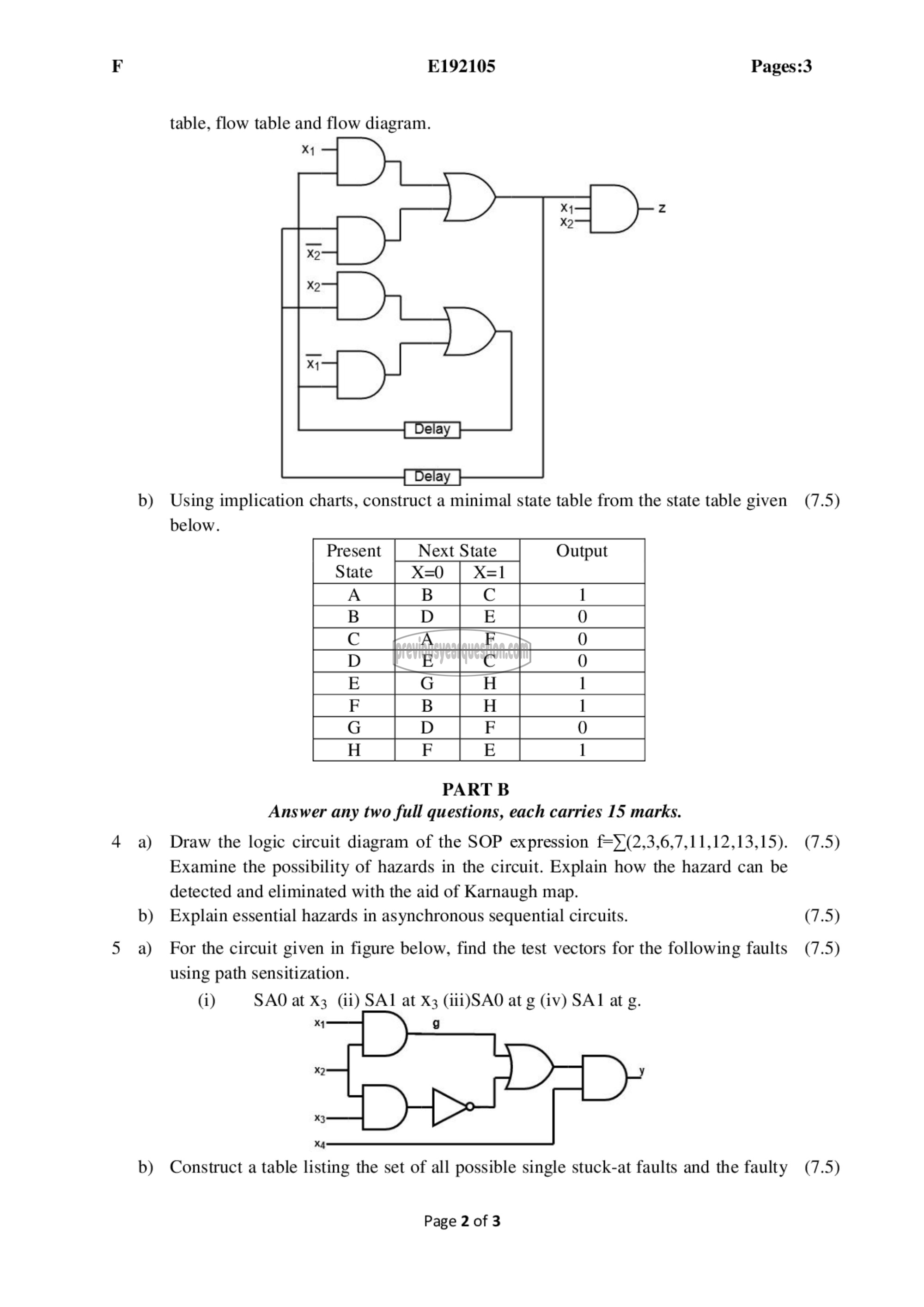

table, flow table and flow diagram.

b) Using implication charts, construct a minimal state table from the state table given

below.

PART 13

Answer any two full questions, each carries 15 marks.

4 a) Draw the logic circuit diagram of the SOP expression 1) (2,3,6,7.11,12,13,15).

Examine the possibility of hazards in the circuit. Explain how the hazard can be

detected and eliminated with the aid of Karnaugh map.

b) Explain essential hazards in asynchronous sequential circuits.

5 a) For the circuit given in figure below, find the test vectors for the following faults

using path sensitization.

(i) SAO at X3 (ii) SAI at X3 (iii)SAO at ع (iv) ൭൧1 at 8.

x {+न

×4

(7.5)

(7.5)

(7.5)

(7.5)

b) Construct a table listing the set of all possible single stuck-at faults and the faulty (7.5)

Page 2 of 3