APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 2

Subject : Parallel Computer Architecture

Year : 2018

Term : MAY

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : 01 CS 6102

Page:1

4.

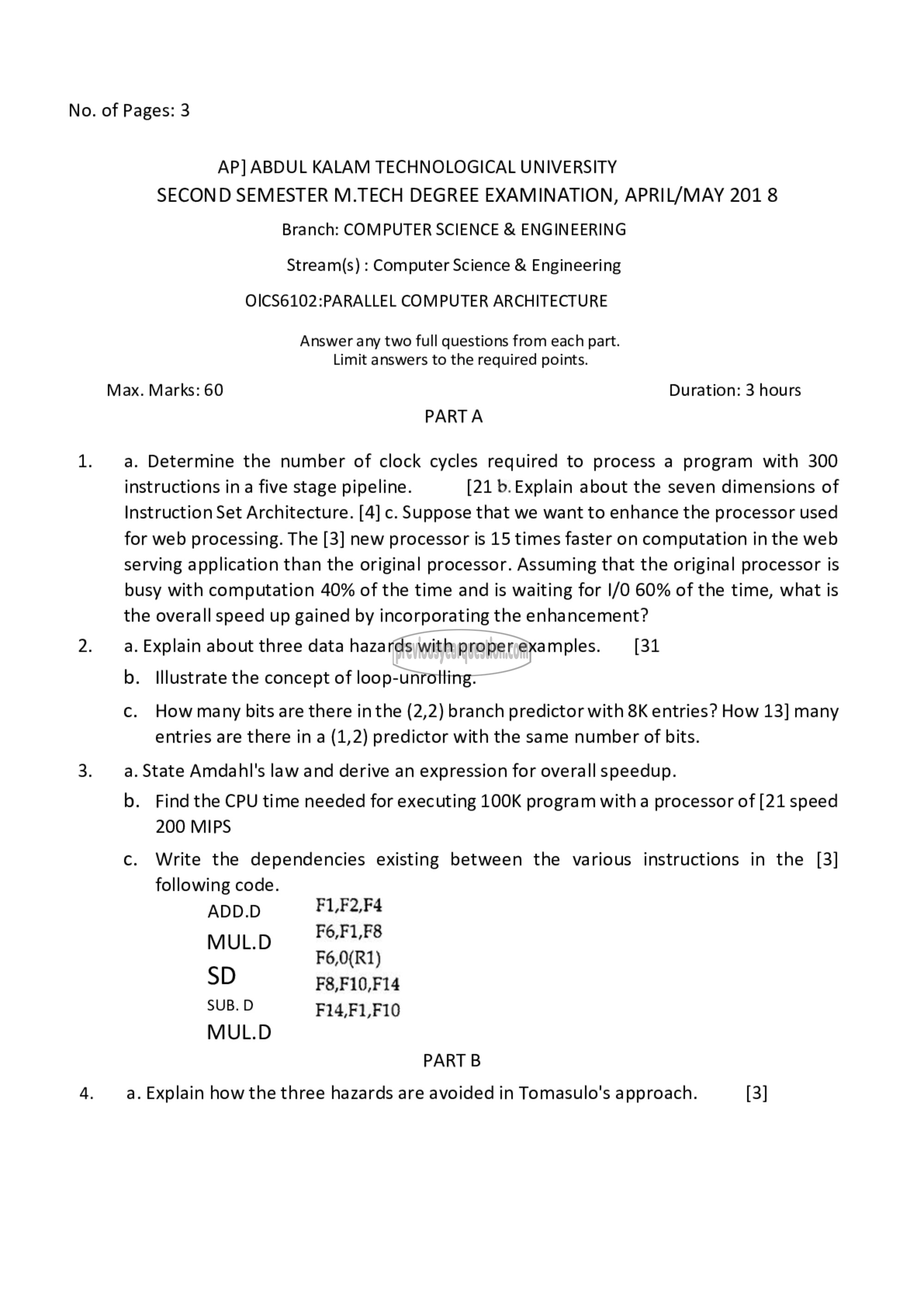

. of Pages: 3

AP] ABDUL KALAM TECHNOLOGICAL UNIVERSITY

SECOND SEMESTER M.TECH DEGREE EXAMINATION, APRIL/MAY 201 8

Branch: COMPUTER SCIENCE & ENGINEERING

Stream(s) : Computer Science & Engineering

OICS6102:PARALLEL COMPUTER ARCHITECTURE

Answer any two full questions from each part.

Limit answers to the required points.

Max. Marks: 60 Duration: 3 hours

PARTA

a. Determine the number of clock cycles required to process a program with 300

instructions ina five stage pipeline. [21 b. Explain about the seven dimensions of

Instruction Set Architecture. [4] c. Suppose that we want to enhance the processor used

for web processing. The [3] new processor is 15 times faster on computation in the web

serving application than the original processor. Assuming that the original processor is

busy with computation 40% of the time and is waiting for |/0 60% of the time, what is

the overall speed up gained by incorporating the enhancement?

a. Explain about three data hazards with proper examples. [31

0. Illustrate the concept of loop-unrolling.

c. Howmany bits are there inthe (2,2) branch predictor with 8K entries? How 13] many

entries are there in a (1,2) predictor with the same number of bits.

a. State Amdahl's law and derive an expression for overall speedup.

0. Find the CPU time needed for executing 100K program with a processor of [21 speed

200 MIPS

c. Write the dependencies existing between the various instructions in the [3]

following code.

ಟ್ 111.

MULD FOFLES

F6,0(R1)

SD F8,F10,F14

SUB. 0 F14,F1,F10

MUL.D

PART B

a. Explain how the three hazards are avoided in Tomasulo's approach. [3]