APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 2

Subject : Design of VLSI Systems

Year : 2017

Term : APRIL

Scheme : 2015 Full Time

Course Code : 01 EC 6122

Page:1

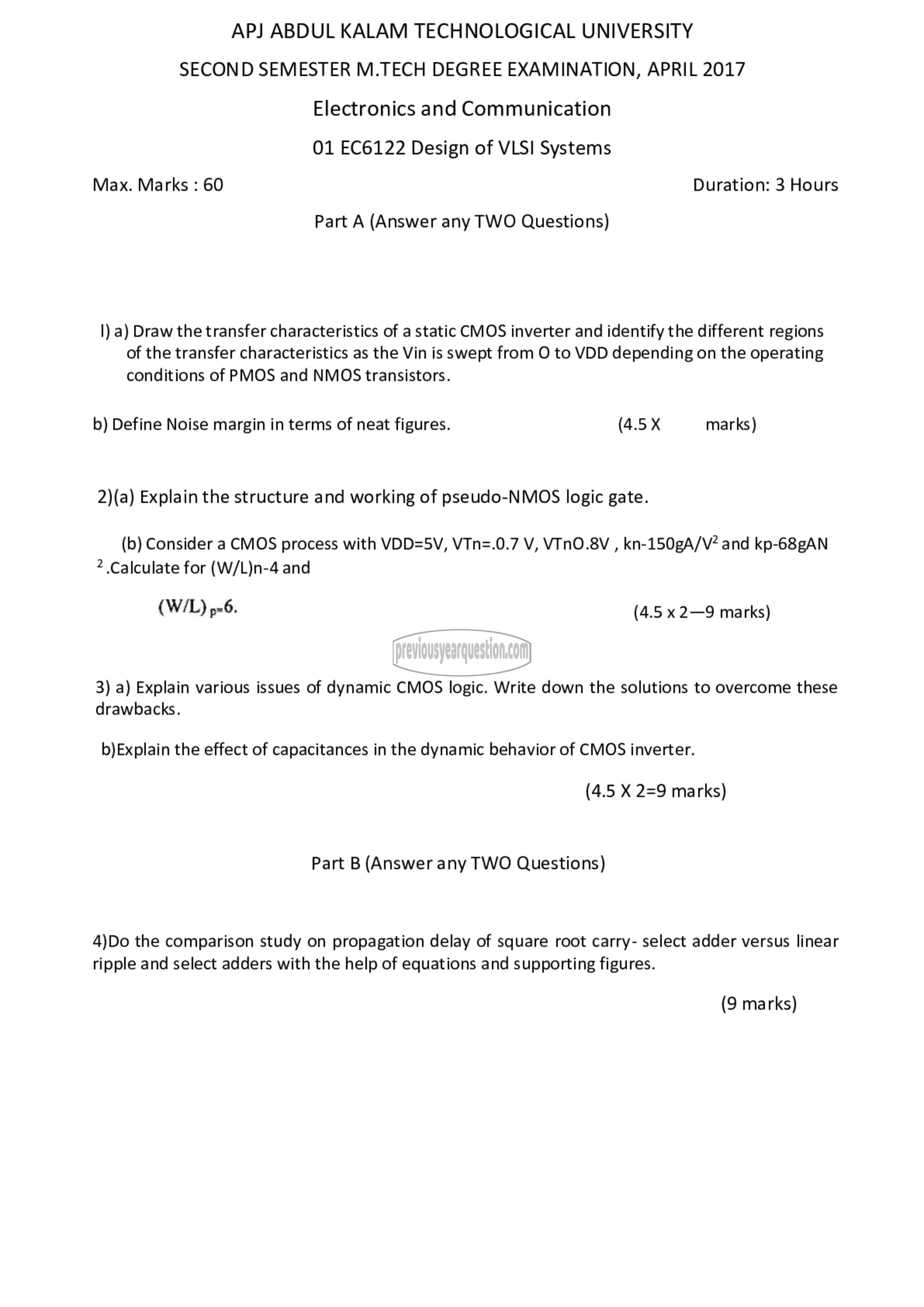

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

SECOND SEMESTER M.TECH DEGREE EXAMINATION, APRIL 2017

Electronics and Communication

01 EC6122 Design of VLSI Systems

Max. Marks : 60 Duration: 3 Hours

Part A (Answer any TWO Questions)

|) ೩) Draw the transfer characteristics of a static CMOS inverter and identify the different regions

of the transfer characteristics as the Vin is swept from O to VDD depending on the operating

conditions of PMOS and NMOS transistors.

b) Define Noise margin in terms of neat figures. (4.5% marks)

2)(a) Explain the structure and working of pseudo-NMOS logic gate.

(0) Consider a CMOS process with VDD=5V, VTn=.0.7 ५, VTnO.8V , kn-150gA/V? and kp-68gAN

2 Calculate for (W/L)n-4 and

(W/L) 6۰۔م (4.5 x 2—9 marks)

3) a) Explain various issues of dynamic CMOS logic. Write down the solutions to overcome these

drawbacks.

b)Explain the effect of capacitances in the dynamic behavior of CMOS inverter.

(4.5 X 2=9 marks)

Part B (Answer any TWO Questions)

4)Do the comparison study on propagation delay of square root carry- select adder versus linear

ripple and select adders with the help of equations and supporting figures.

(9 marks)