APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 6

Subject : Embedded System

Year : 2018

Term : MARCH

Scheme : 2015 Full Time

Course Code : EC 308

Page:84

y ⋅∡⋅⋅⊳≱

0 ಕಡ "तत्त न्क््ल््तवा- റ തട

me that the data transfer is to occur between hard disk system memory. The DMA is used in that

When the I/Os are needed for large amount data from a peripheral device to the memory Aaddresse

system or large amount of data is to be transferred by the I/Os, the interrupt-based mechanism is no

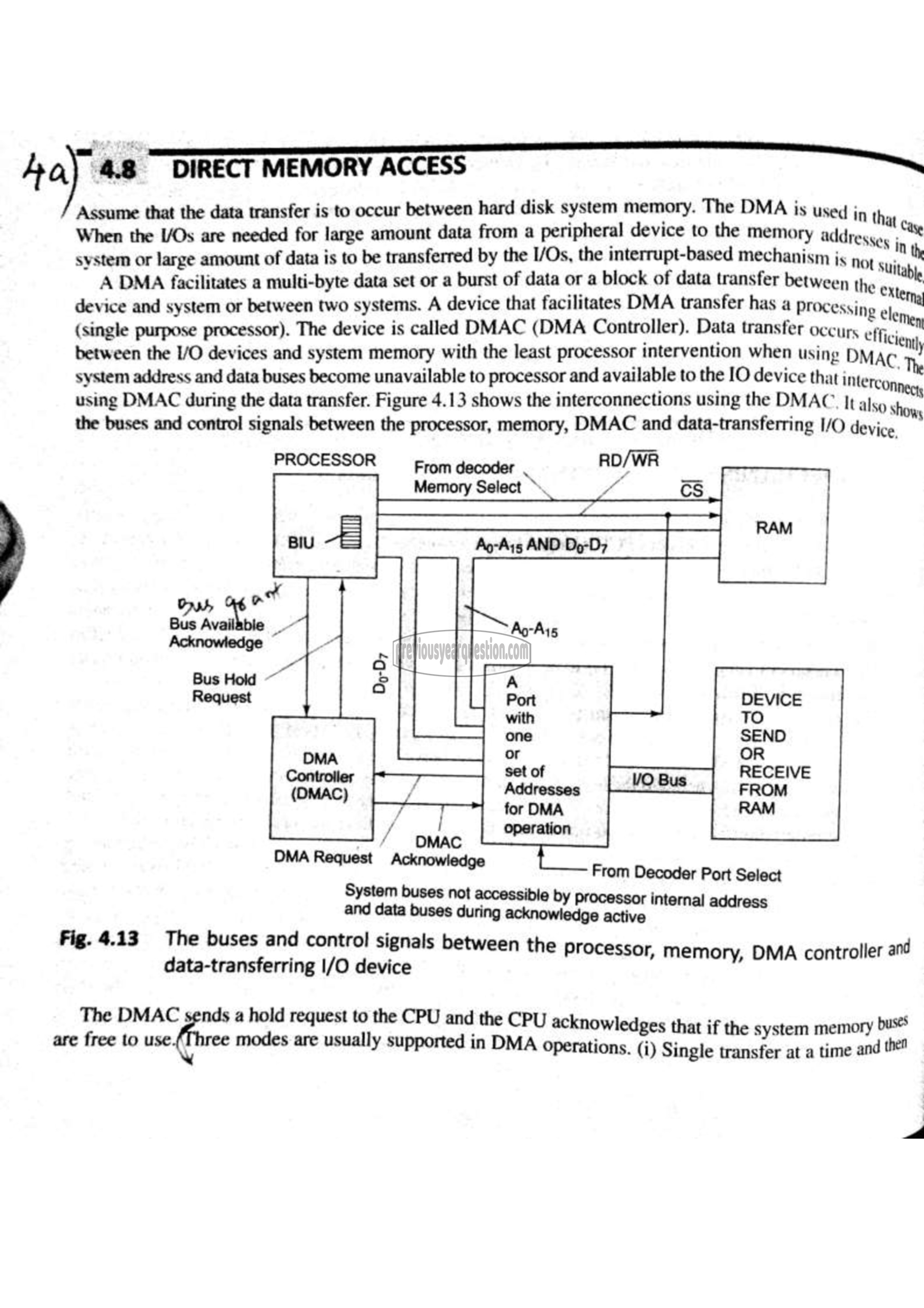

"A DMA facilitates a multi-byte data set or a burst of data or a block of data transfer between the Chen,

device and system or between two systems. A device that facilitates DMA transfer has a Processing ele

(single purpose processor). The device is called DMAC (DMA Controller). Data transfer occurs efficieny

between the 1/0 devices and system memory with the least processor intervention when using DM AC. )

system address and data buses become unavailable to processor and available to the 10 device that intercon

using DMAC during the data transfer. Figure 4.13 shows the interconnections using the DMAC. It also ತ

the buses and control signals between the processor, memory, DMAC and data-transferring I/O device

PROCESSOR ನ್ಯ decoder RD/WR

Memory Select ٠ va cs

58 in

Suj

BIU = 4-5 AND 00-07

DEVICE

TO

ள்

र

cay de அர்த்த

Acknowledge

Bus Hold >

Request

DMA

Controller

RECEIVE

FROM

RAM

(DMAC)

From Decoder Port Select كيه

System buses not accessible int

and data buses during ದ್ internal address

Fig. 4.13 The buses and control signals between the processor, memory, DMA controller and

data-transferring ۱/۵ device

The ய் sends a hold request to the CPU and the CPU acknowledges that if the system memory 0४

are free to use.(Three modes are usually supported in DMA operations. (i) Single transfer at a time and the"