APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 6

Subject : Embedded System

Year : 2018

Term : MARCH

Scheme : 2015 Full Time

Course Code : EC 308

Page:80

Whee

A processor provides for one of the following ۲۴۶ of uring the

ISR VECTADDR hased 3. ६

“வு

mechanism.

Processor Vector Address

tw

Fig. 4.6 (०) ISR_VECTADDRs for hardware inter

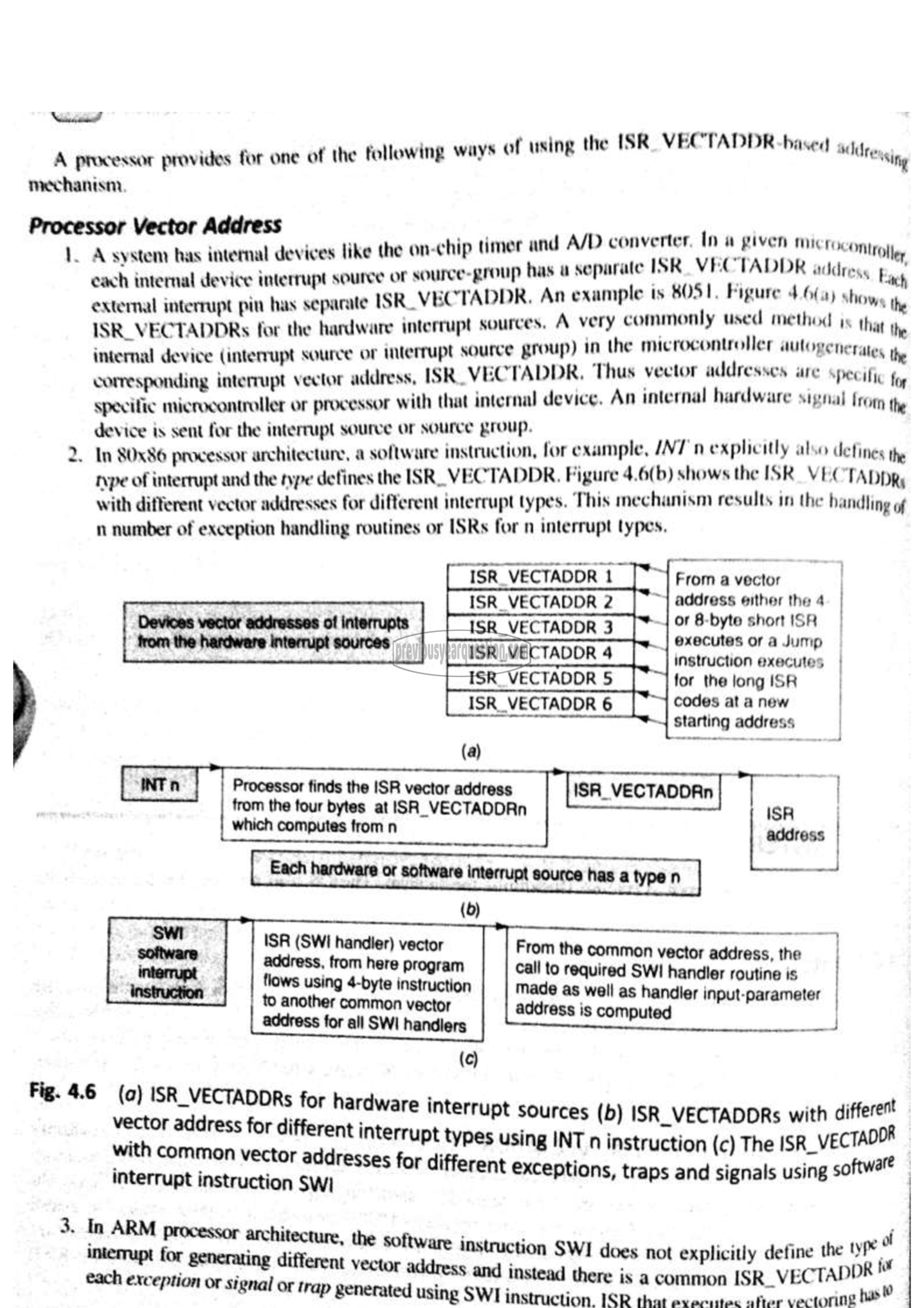

A system has internal devices like the on-chip timer and A/D CONVERT. In ഇ 1110110೧೧೧,

cach internal device interrupt source of source-group has ५ separate ISR ஹம் ADDR address bach

external interrupt pin has രം ISR_VECTADDR, An example ts 8051. Figure 4 6/4) shows |

18% VECTADDRs for the hardware interrupt sources, A very commonly Used Method ۱× thar the

internal device (interrupt source نه 1111011110! source group) in the microcontroller aulogeneraies the

corresponding interrupt vector address, ISR. VECTADDR, Thus vector addresses ate specif 7

specific microcontroller or processor with that internal device. An internal hardware signal {rom the

device is sent for the interrupt source or source group.

. In 80x86 processor architecture, a software instruction, for example, /N7 م explicitly also defines the

type of interrupt and the type defines the ISR_VECTADDR., Figure 4.6(b) shows the 181९ VECTADDR,

with different vector addresses for different interrupt types. This mechanism results in the handling of

n number of exception handling routines or 158% for n interrupt 1905,

From a vector

ISR VECTADDR ட

ISR_VECTADDR 2 address either the 4

Devices vector addresses of interrupts ISR VECTADDR 3 | or 8-byte short ISA

from the hardware interrupt sources executes or a Jump

ISR_VECTADDR 4

ISR_VECTADOR 5

iNStructiOn executes |

for the long ISR |

codes at a new |

Starting address

(a)

| कषा? । Processor finds the ISR vector address

from the tour bytes at ISR_VECTADDRn

which computes from n | ५ Gites |

Each hardware or software interrupt source has a type م താത്

(0)

ISR (SWI handler) vector From the com ess,the |

mon vector address, the |

address. from here program Call to required SWI handler routine is |

0 using 4-byte instruction made as well as handler input-parameter |

another common vector address is computed

address for all SWI handlers ٠

(0)

rupt sources (0) ISR_VECTADDRs with different

vector address for different interrupt | i i 78

with common vector addresses fo Pt types using INT n instruction (८) The ISR_VECTAD

: r di ∙ 4 ⋅ 0

ಕರಗದು instruction Saf different exceptions, traps and signals using softwa

instead > ECT for

ടും ress and i there is a common ISR_VECTADDK

7 signal or ‘rap generated using SWI instruction. ISR that executes after vectors has