APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Logic Circuit Design

Year : 2018

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EC 207

Page:2

b) Explain a MOD 6 asynchronous counter using J K Flip Flop (7)

6 a) Design a 3-bit synchronous counter using D Flip Flop (10)

b) Convert SR Flip Flop into J K Flip Flop (5)

PARTC

Answer any two full questions, each carries20 marks.

7 a) Draw the logic diagram of 3 bit PIPO shift register with LOAD/SHIFT control and(10)

explain its working.

b) Explain Moore and Mealy machine models. Compare the models (10)

8 9) Draw the logic diagram of 3 —bit Johnson counter and explain the working with (10)

truth table.

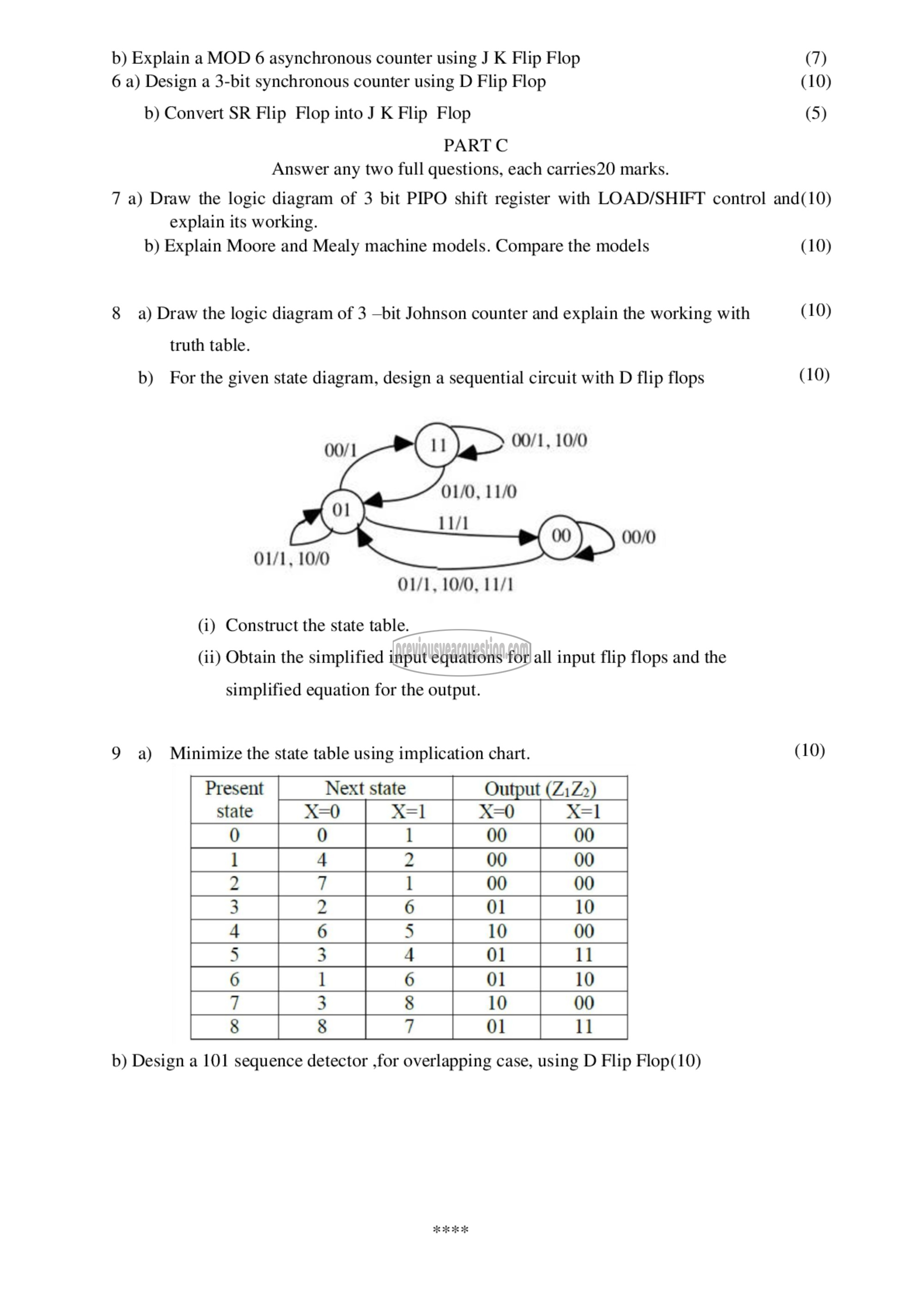

b) For the given state diagram, design a sequential circuit with D flip flops (10)

01/1, 10/0

01/1, 10/0, 11/1

(i) Construct the state table.

(ii) Obtain the simplified input equations for all input flip flops and the

simplified equation for the output.

9 a) Minimize the state table using implication chart. (10)

b) Design a 101 sequence detector ,for overlapping case, using D Flip Flop(10)