APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Switching Theory and Logic Design

Year : 2017

Term : JULY

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : CS 203

Page:1

6

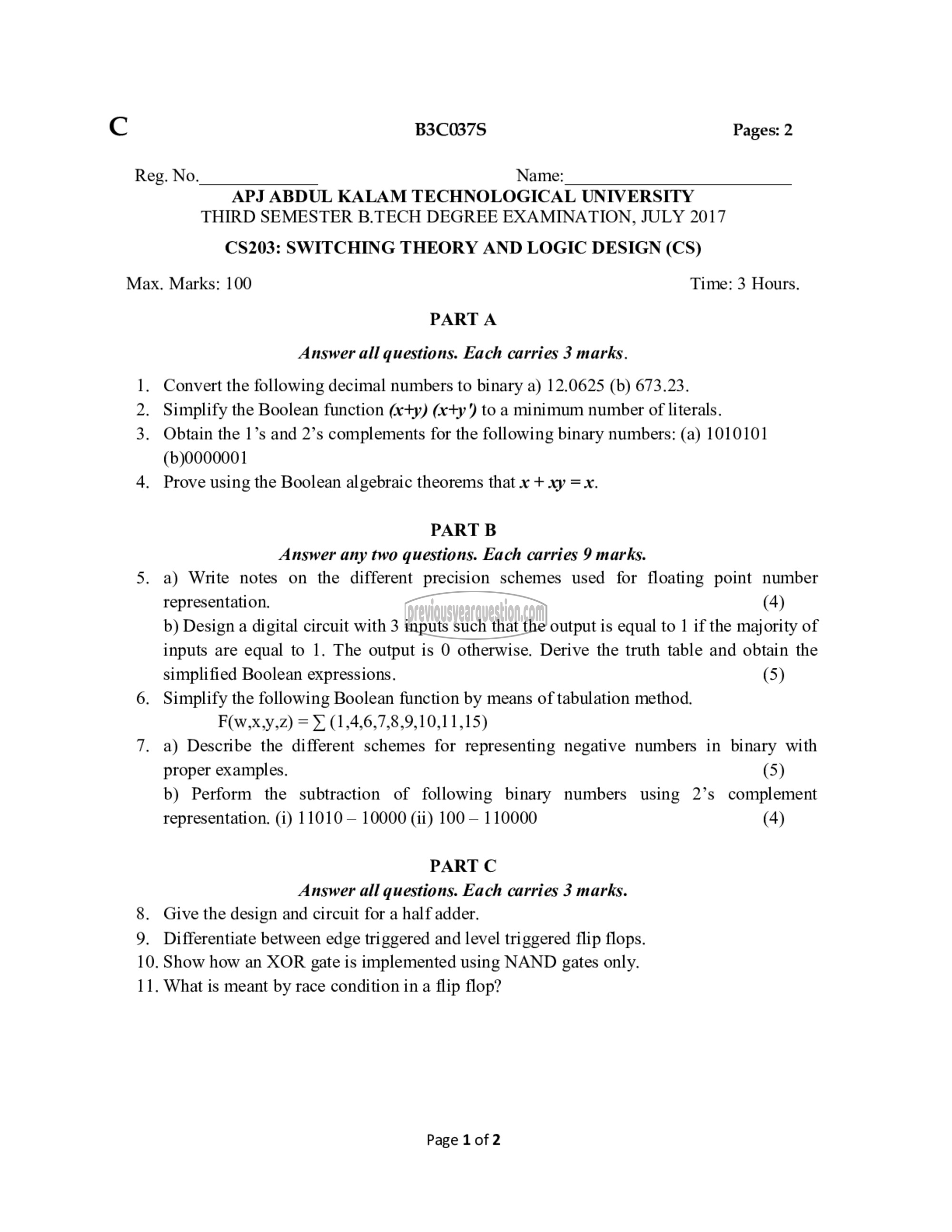

Reg. No. Name:

B3C037S Pages: 2

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

THIRD SEMESTER B.TECH DEGREE EXAMINATION, JULY 2017

CS203: SWITCHING THEORY AND LOGIC DESIGN (CS)

Max. Marks: 100 Time: 3 Hours.

8.

9

PART A

Answer all questions. Each carries 3 marks.

Convert the following decimal numbers to binary a) 12.0625 (b) 673.23.

Simplify the Boolean function (x+y) (x+y) to a minimum number of literals.

Obtain the 1’s and 2’s complements for the following binary numbers: (a) 1010101

(b)0000001

Prove using the Boolean algebraic theorems that x + xy =x.

PART B

Answer any two questions. Each carries 9 marks.

a) Write notes on the different precision schemes used for floating point number

representation. (4)

b) Design a digital circuit with 3 inputs such that the output is equal to 1 if the majority of

inputs are equal to 1. The output is 0 otherwise. Derive the truth table and obtain the

simplified Boolean expressions. (5)

Simplify the following Boolean function by means of tabulation method.

F(w,x,y,z) = © (1,4,6,7,8,9,10,11,15)

a) Describe the different schemes for representing negative numbers in binary with

proper examples. (5)

b) Perform the subtraction of following binary numbers using 2’s complement

representation. (1) 11010 — 10000 (11) 100 — 110000 (4)

PART C

Answer all questions. Each carries 3 marks.

Give the design and circuit for a half adder

Differentiate between edge triggered and level triggered flip flops

10. Show how an XOR gate is implemented using NAND gates only.

11. What is meant by race condition in a flip flop?

Page 1 of 2